Other Parts Discussed in Thread: TPS563219A, TPS563208, TPS62136, TIDA-01423

Hi team.

My customers are looking for the inverting power supply of the specification below.

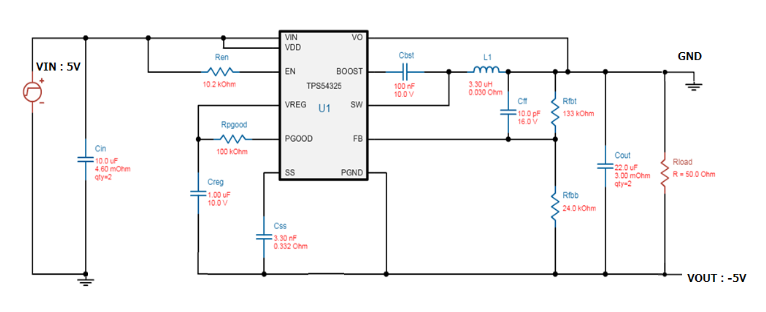

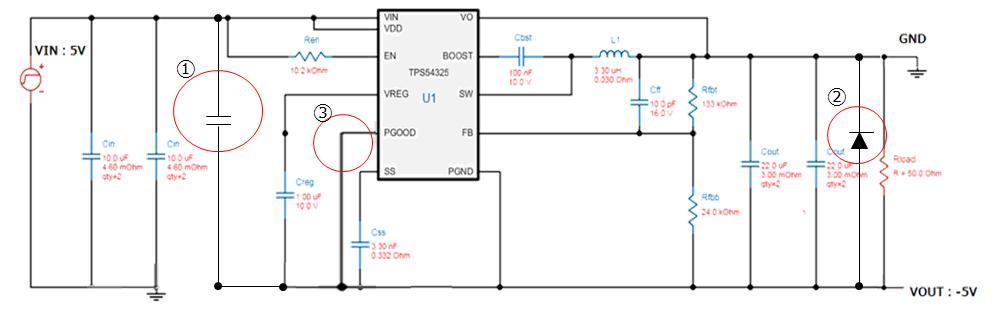

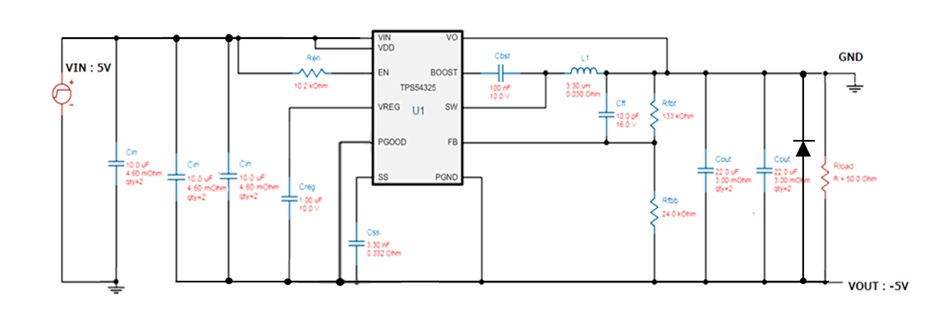

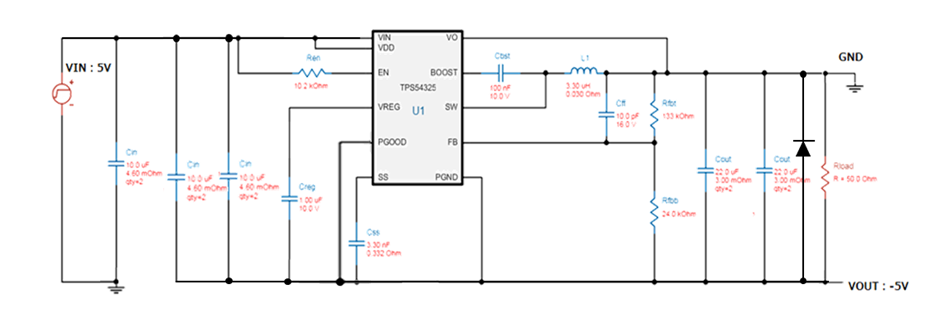

Specification:5.0V ⇒ - 5.0V / 0.1A

We were promotioning negative power supply DC / DC and charge pump,

It was said that this time it can not be adopted unless it is a device with parts registration at the customer.

So TPS54325 is registration parts, I got a comment that it might be usable if proposed by inverting buck-boost circuit.

And, to consider, I was told that I would like examples of circuit diagrams on this device.

So please.

I changed the wiring based on the circuit simulating 10 V ⇒ 5.0 V / 0.1 A at WEBENCH and I was create the circuit diagram.

Would you please let me know if you can present it to customers with this circuit including the peripheral constant?

(Could you verify it ?)

※Correct it if there is a mistake, It'll be helpfull me.

Best regards,

Masumi Sekiguchi