Hi expert,

Customer has an issue on their project. They found out there are three power rails fail to power on but other rails are all okay. As we know, TPS650944 should power on every power rail follow the power sequence. But VNN is not okay and other rails powered on is not reasonable. Would you kindly help to suggest any clue to figure out this question? Thanks a lot!!

No power : VNN, VCCRAM, VCCGI,

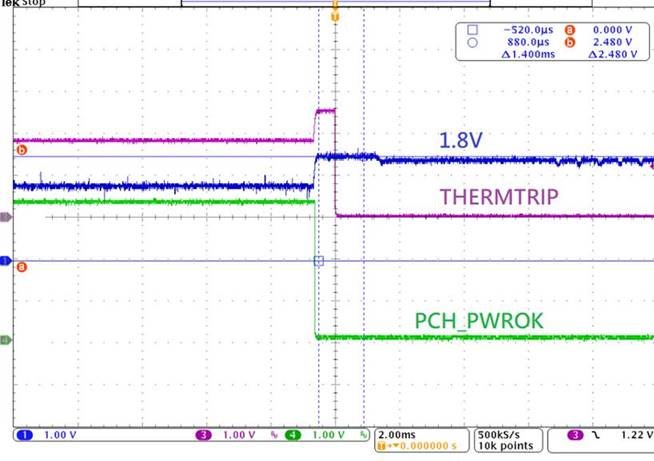

THERMTRIPB is keep 2V.

Best regards,

Ann Lien