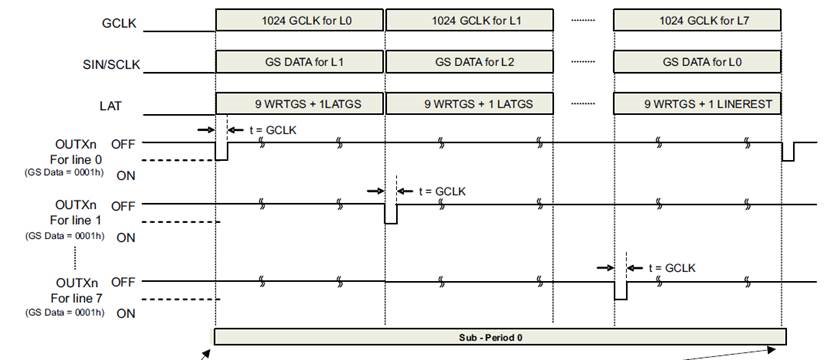

From spec. description, we need to input 2^N clock in one sub-period for one Line as GSCLK.

What will it effect If we input more than 2^N clock? (OUTXn turn off?)

In practice, it's easy to input GSCLK with "fix frequency" and hard to input with "fix clock count".

Do you have any suggestion about this situation?