Other Parts Discussed in Thread: TIDA-010074

Hi

I have some queries about TIDA-010074

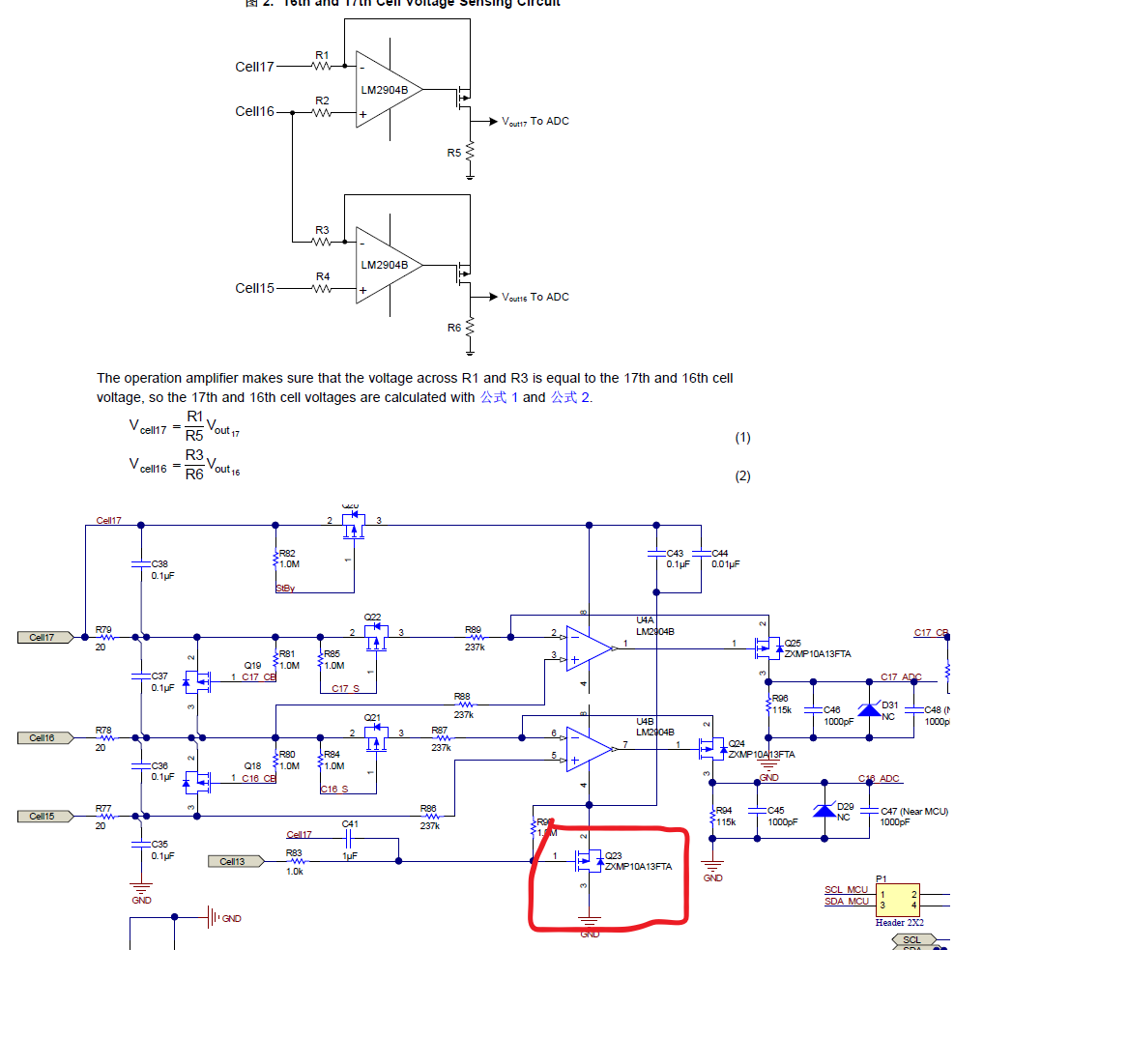

1. VDD of the op amp is CELL17+, VSS is CELL13+, and a 1M resistance between VSS and CELL13+ will not affect the power supply?What does Q23 do in the schematic diagram?Seems to be off all the time?

2. As shown in the figure, what is the function of P MOS? This connection seems to be different from the usual op amp output to the v-end; How did this formula come out? Vcell16 = R3 / R6 * Vout16

Waiting for your repoy

Thanks

Star