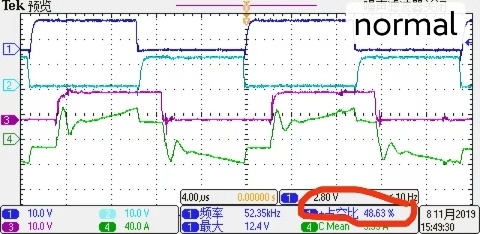

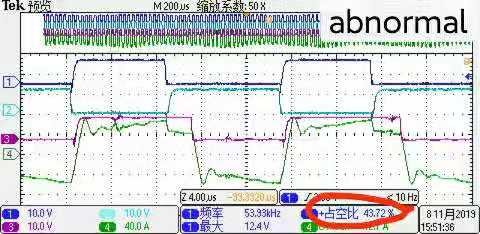

1.Two scope pictures were show as above. As in PSFB DC/DC converter,when the load became larger, for example from 2kW to 2.3kW, the situation became unstable. when it is abnormal, the duty of C and D is 0.42. When it is normal, the duty cycle should be 0.49.

2.Why in unstable situation, the phase shift operation has been lost?

3. I guess that UC3875 has been distorbed when the load changed from 2kW to 2.3kW, so the EAout is also changed. How can I improve this situation?