Hello,

I am using TPS63802 for my Low power device with BLE113 module. I need to power that from Li-ion. So I chose this circuit for stable 3.3V output.

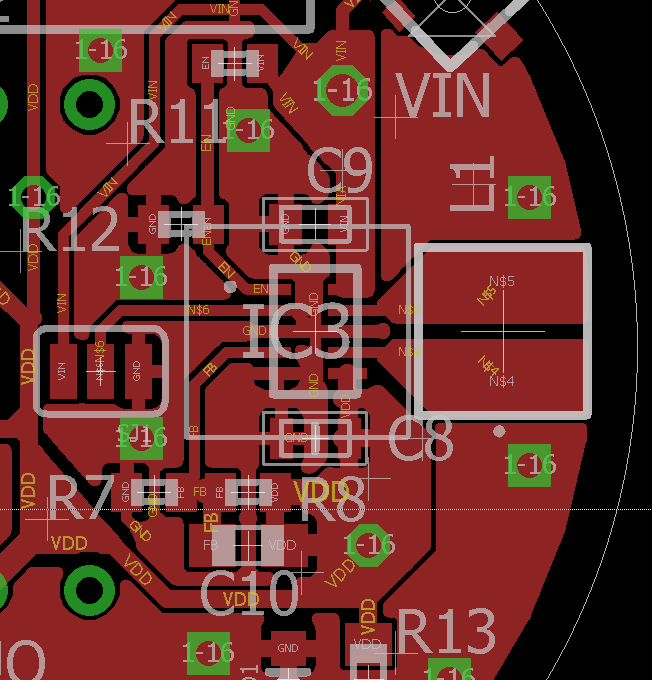

For circuit I used WEBENCH, so all my values corresponds to WEBENCH tool.

My PCB layout is also similar to EVM board

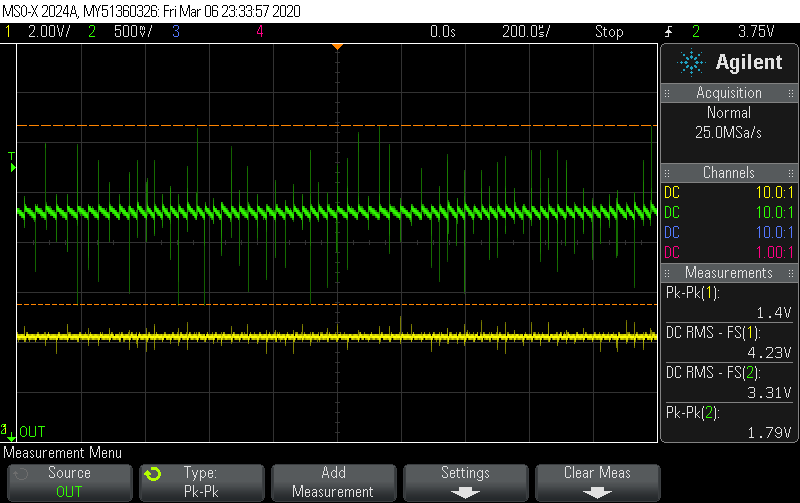

And when I connects the power, the input voltage (Yellow) and the output voltage (green) is shown on my scope as overall signal

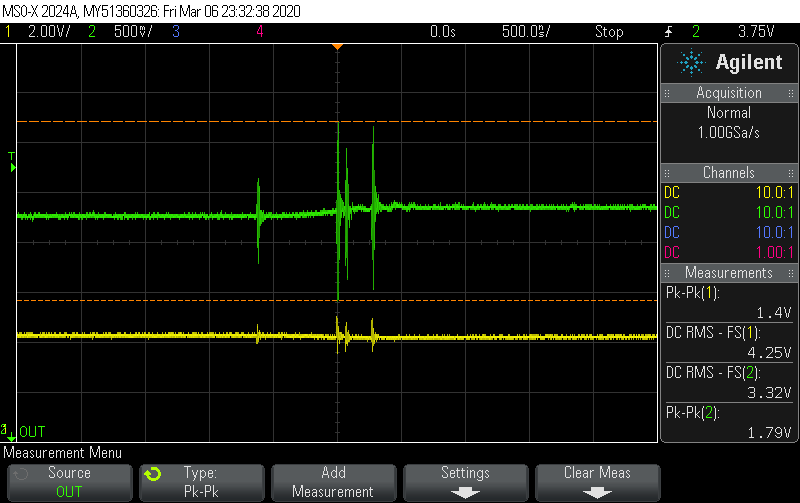

I tried to change input voltages from all the range (4.2V - 3.0V) and I always see the spikes. The zoom of that spikes is on next image.

I tried to add 100nF capacitor on the output close to TPS IC. I tried to use several feedforward capacitor ranging from 1pF to 100pF paralel to my R8 resistor (from output to FB pin).

I found in datasheet of BLE113, that it allows voltage ripple less than 10mV. And I don't know how to smooth the output voltage.

Do you have any suggestion please?

Regards

dbarvik