Hi Team,

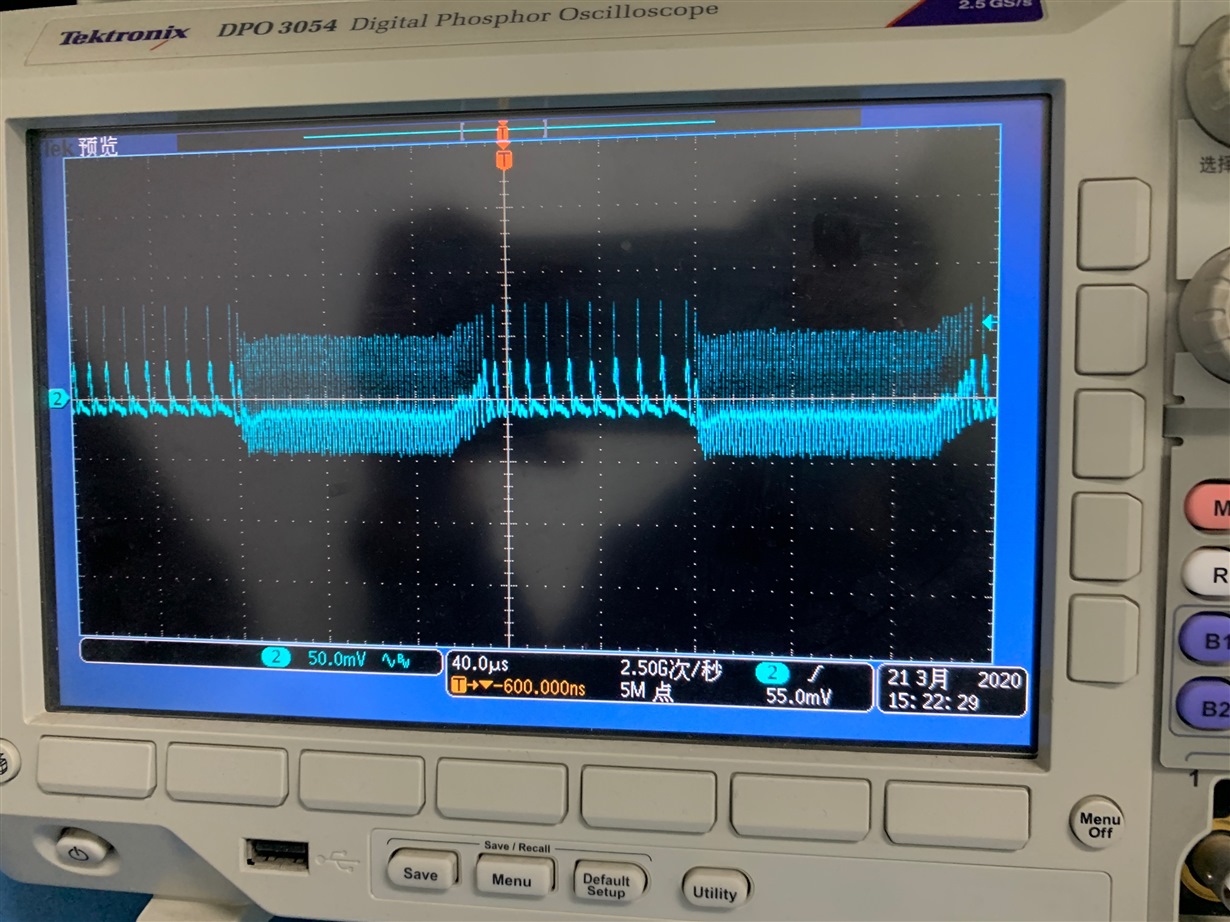

While I was testing TPS53219A's EVM output ripple with the ripple injection cap removed (true DCAP1), the result below. There is an approximately 20mV DC offset between light load and heavy load. It is very strange as DCAP1 should not have any DC offset.

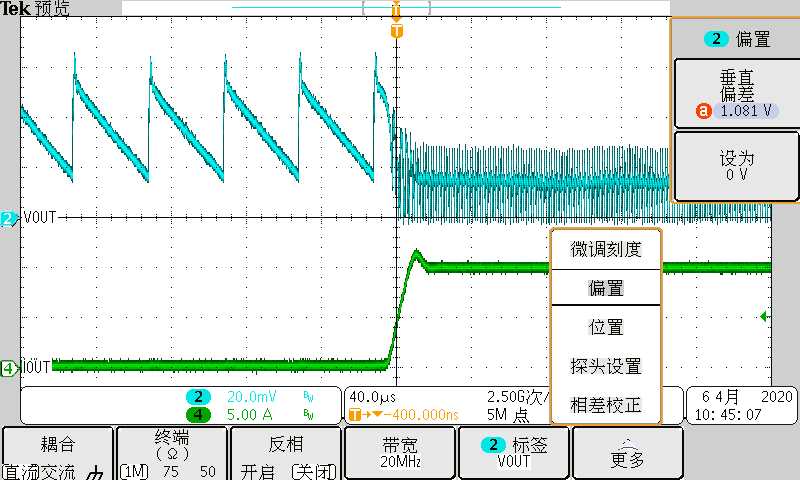

After that, when I turned to EVM user guide, there is no offset though.

I know offset is led by ramp compensation on the reference. According to datasheet, ramp will generate DC offset, so this exists in any load condition. However, it is too strange that test in EVM does not show any DC offset.

Could you please help me point out the reason?

-Wenhao