Hi,

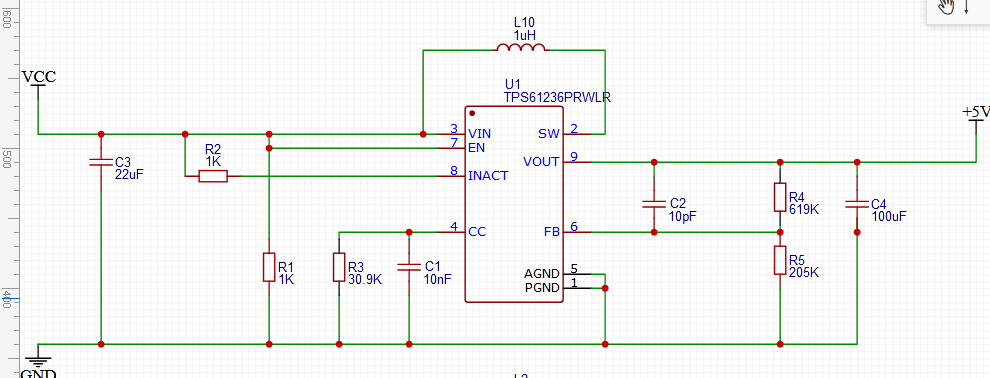

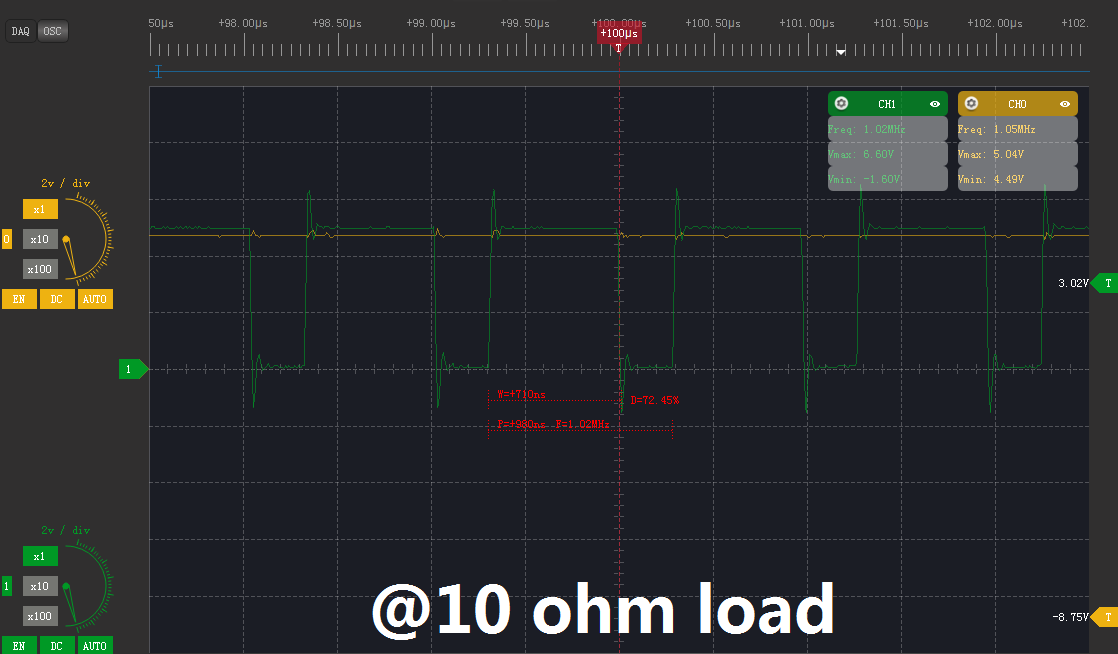

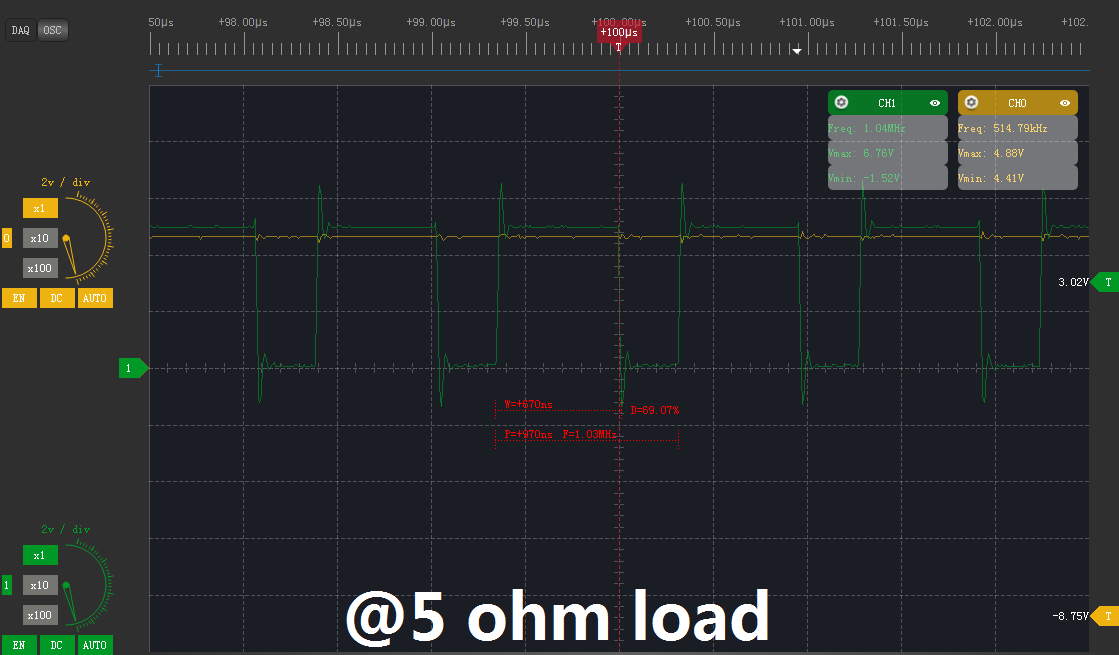

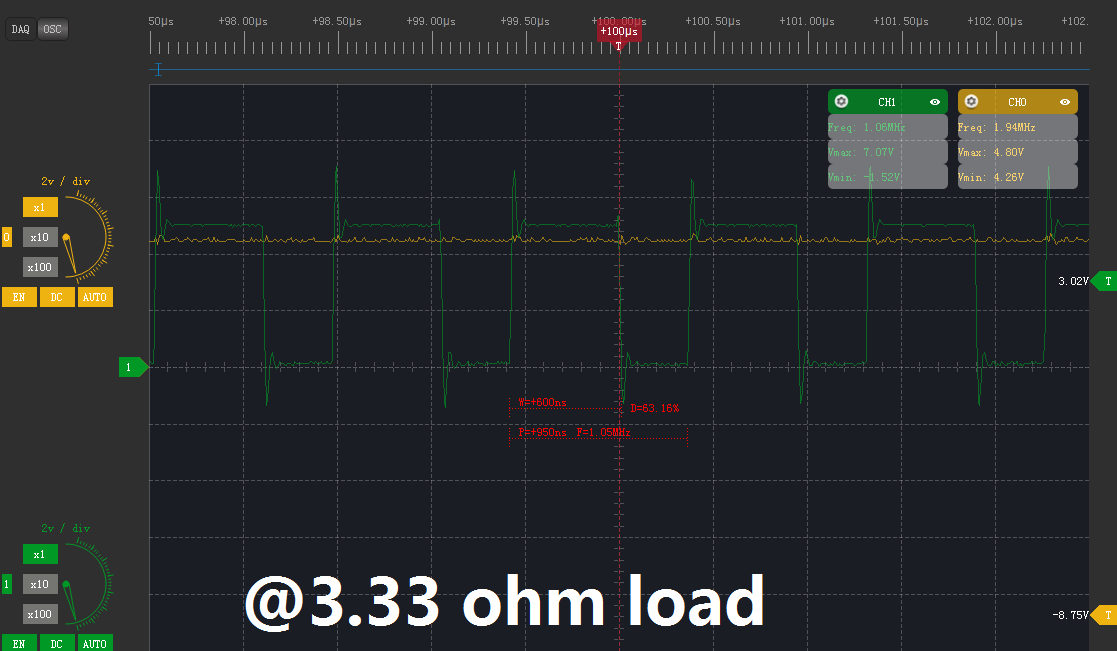

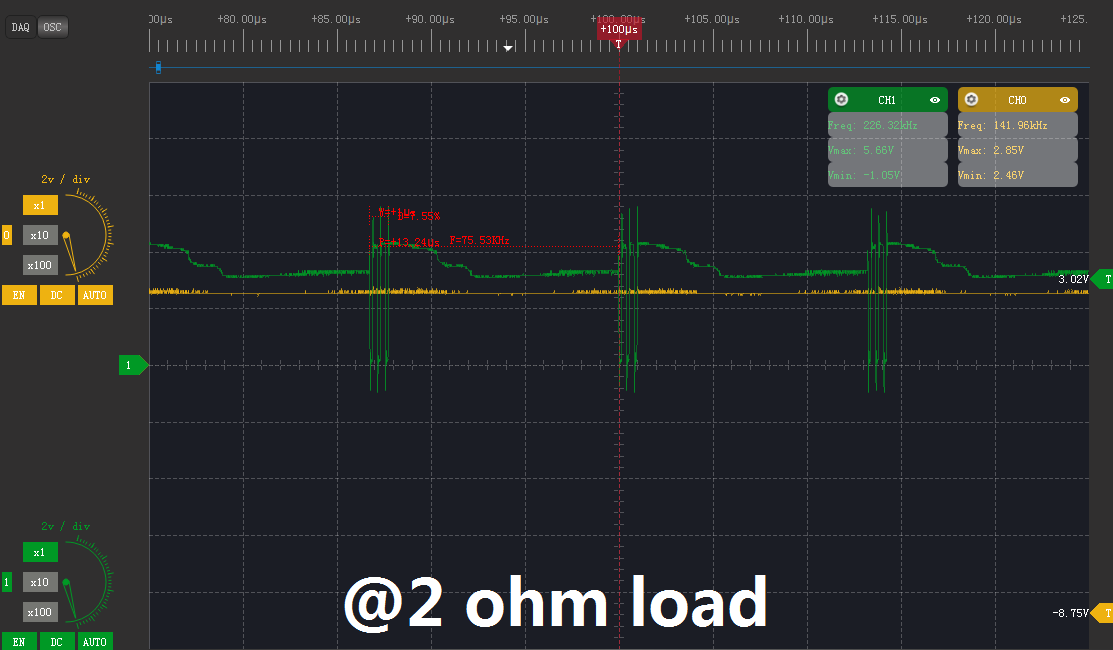

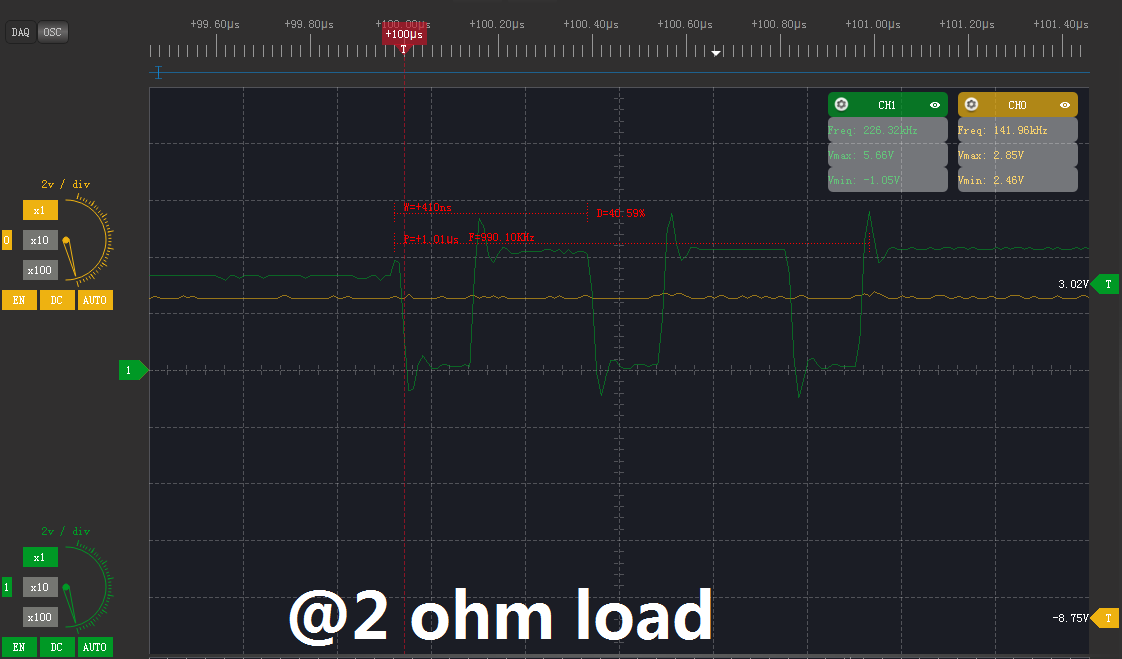

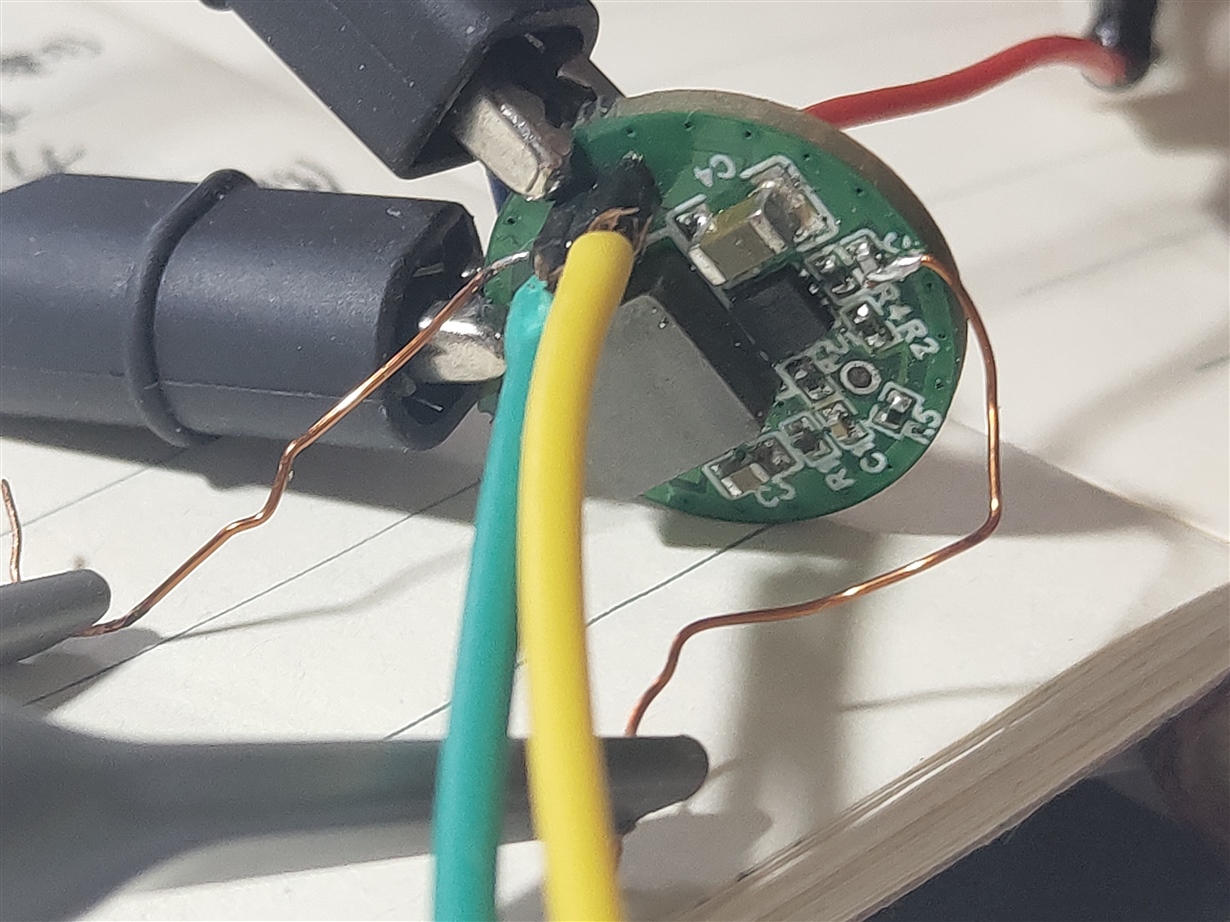

I have built a li-ion to 5V @ 4A constant current DC converter using TPS61236P (the circuit and most of the resistor and capacitor values come from WEBENCH while some changed a little) but it turned out that the output can't reach the set value. I connected a 3.33Ohm resistor as a load, and the current should be 1.5A, but the output current was around 1A and the voltage was around 3.3V ---- even lower than the 3.8V input!

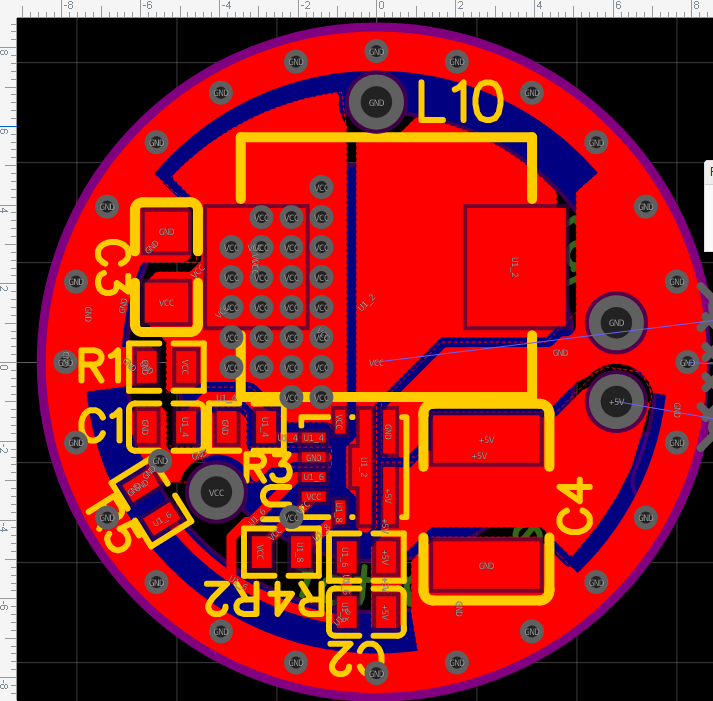

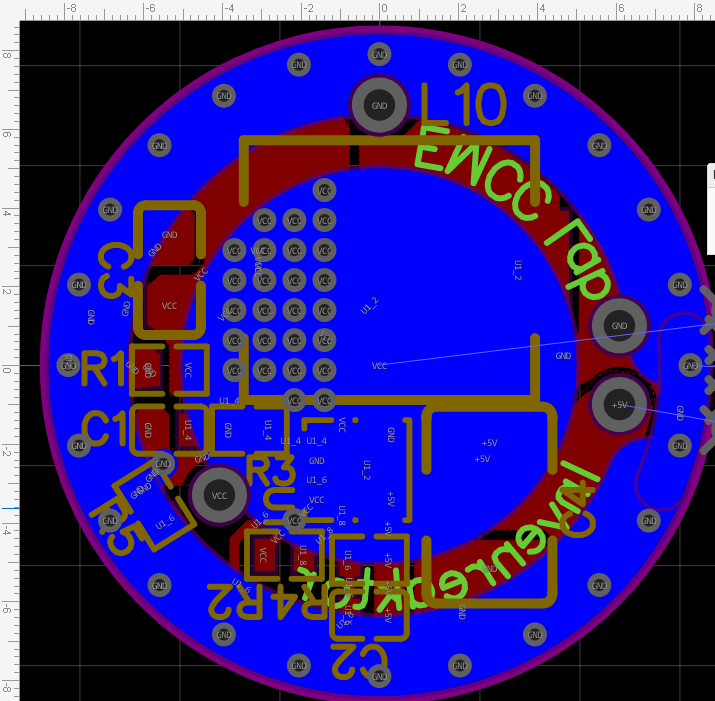

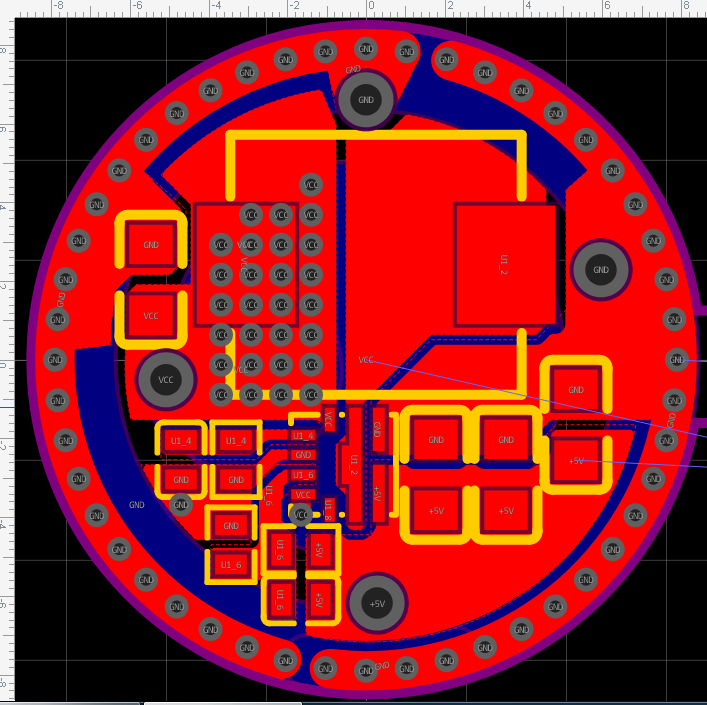

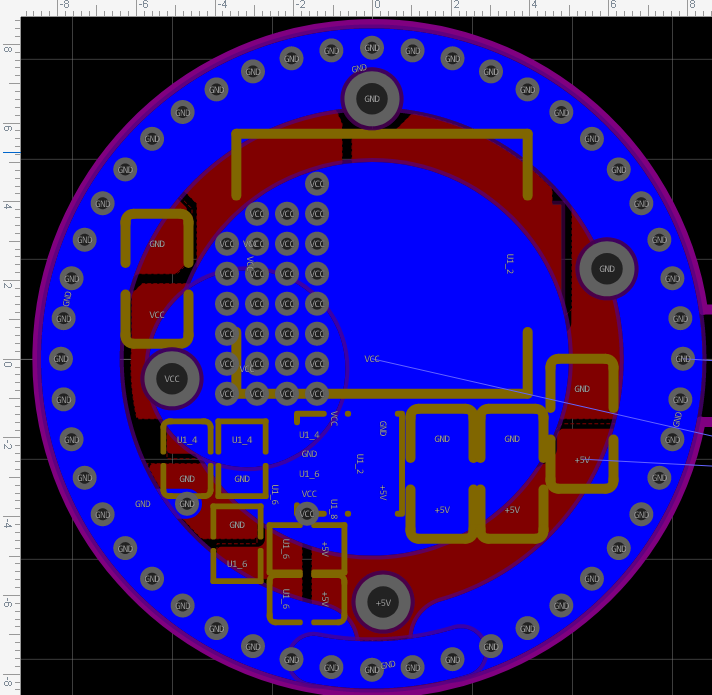

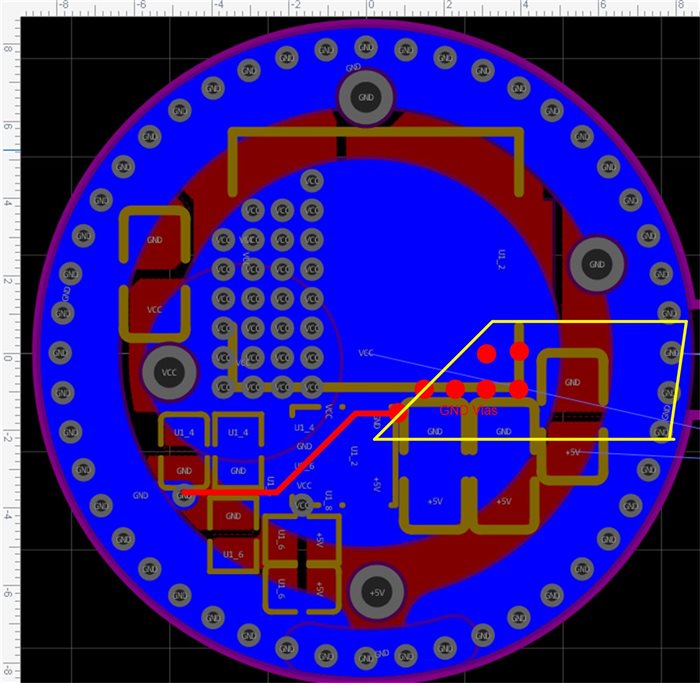

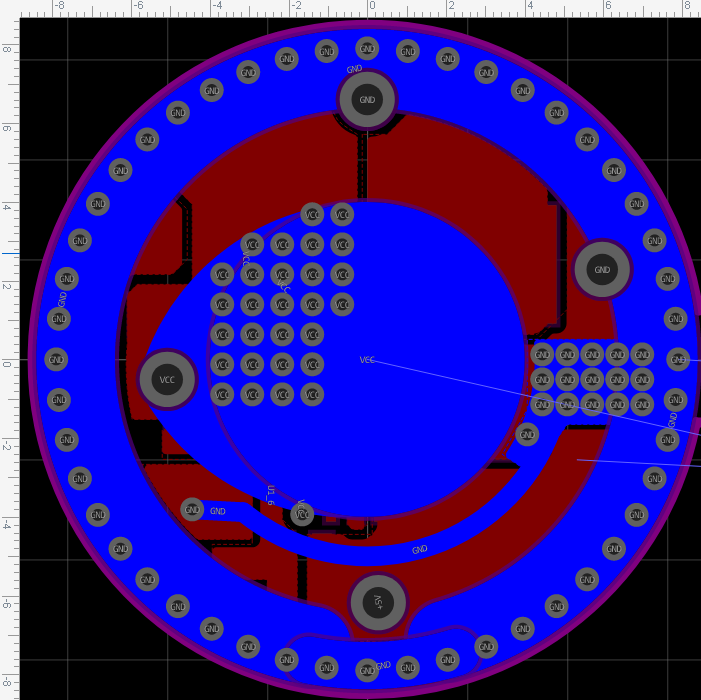

The schematic and both side of the layout are attached.

Thank you so much.