Other Parts Discussed in Thread: LM5025, UCC27200, LM5025B, LM5025A

Dear Expert,

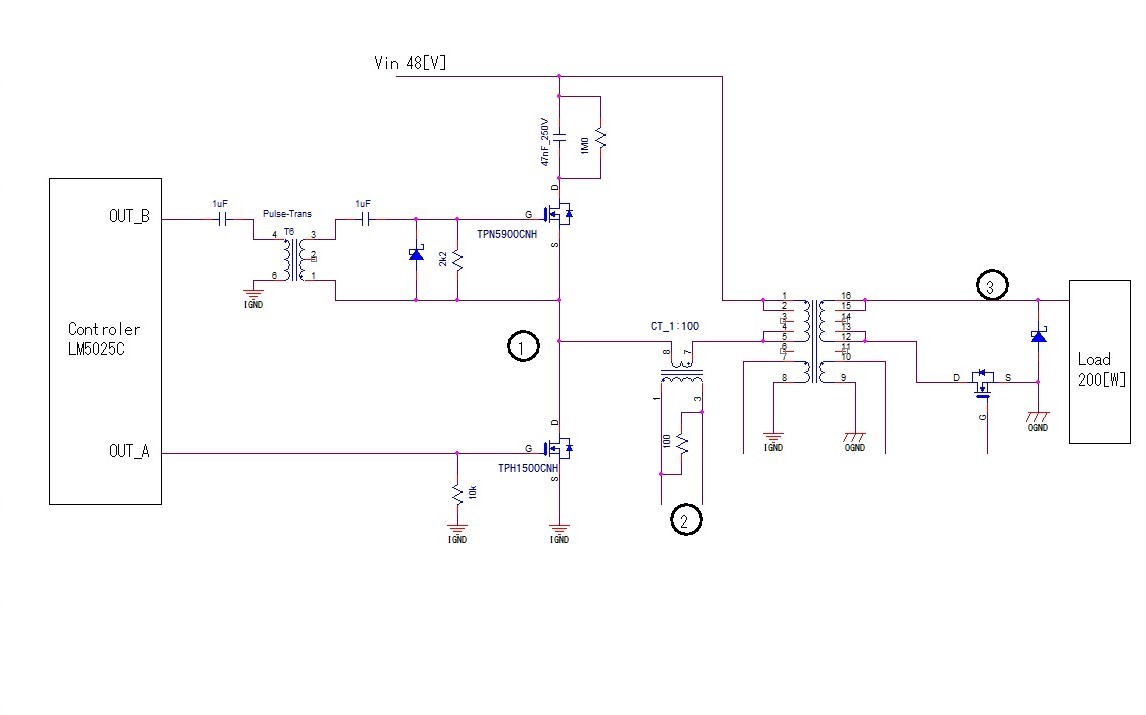

We are using LM5025 and UCC27200 together to Active Clump Converter and worry that UCC27200 has been broken when power down state.

We can not find reasons that PWM duty is increasing when power down, and occurred spike generation on HS of th gate driver over 120V even if we apply 48V Vin.

Attached schematics and Waveforms 1 is observation of broken and another is changed percentage of the load.

I appreciated if you give some suggestions to avoid increasing the duty and / or HS voltage when power down.

regards, Keiichi

.