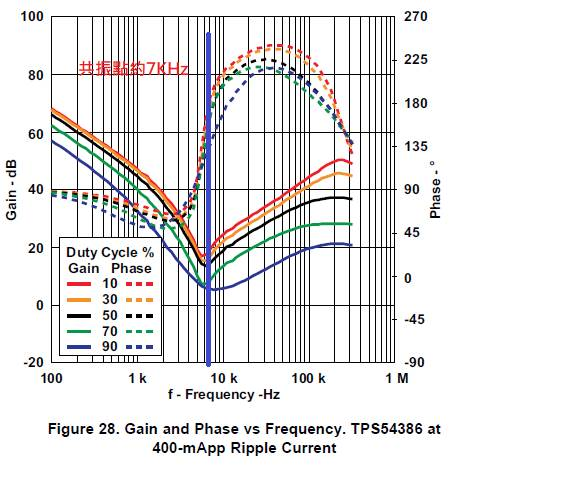

There is an internal compensation in the IC for control loop.

In the calculation example of the datasheet, it seems it doesn't take DC bias of the capacitor into account, correct?

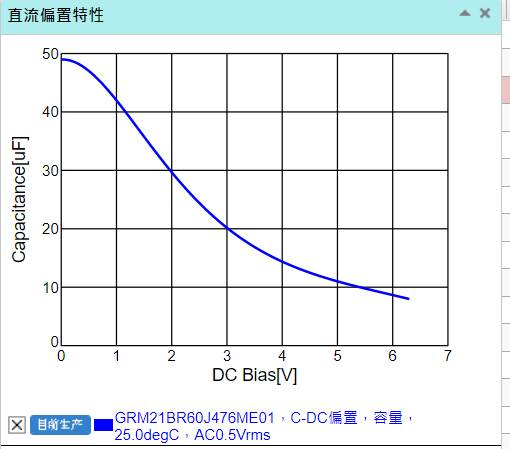

As to the MLCC capacitor material, there is a Typical Characteristics as Capacitance (uF) vs. DC Bias(V). We're wondering to know if it can also lead to the compensation adjustment? Why you didn't take it into account? Very thanks.