Hello,

I designed a Flyback SMPS using UCC28710.

The simplified schematic is below

The divider resistors for vs pin are 82,5k and 27,4k respectively.

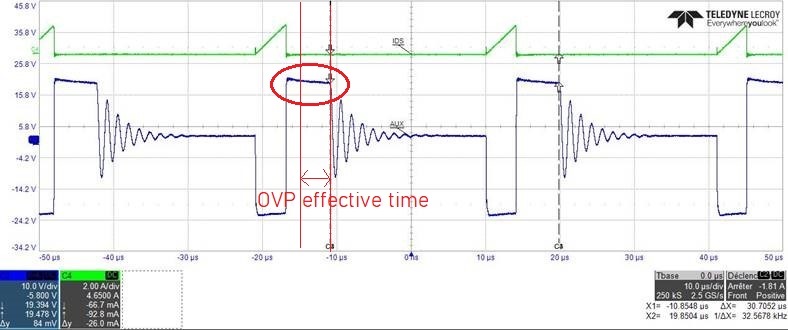

The waveform of the voltage at Vaux is below

The voltage measured at the time secondary winding reaches zero current (as shown) is about 19V.

Then with the resistor divider, the voltage at vs pin is 4,73V (> maximum threshold in the datasheet 4,7V) but there is no overvoltage protection triggered.

Moreover, the OVP function is effective just after the reset of the leakage inductance (2,2us max) and hold during the time of conduction of the secondary diode. The voltage at VS pin during that time is higher than

4,7(V), and there is no protection is triggered.

Could you explain me this conflict?

The measure error is excluded because the probe is calibrated and auto zero.

Regards,