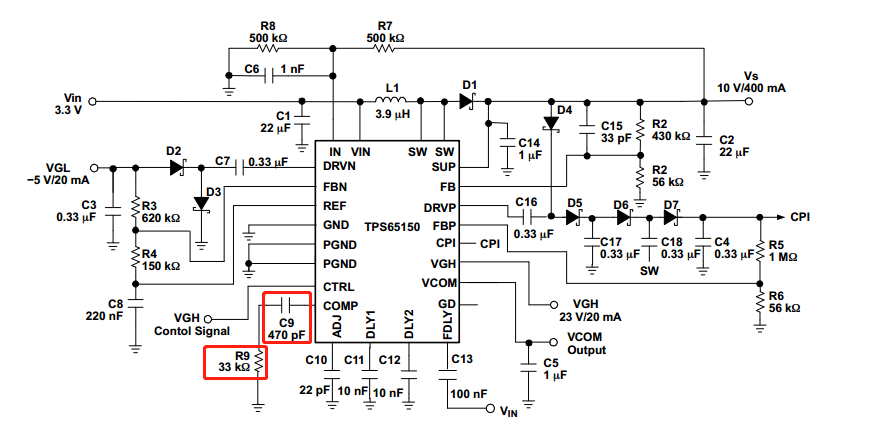

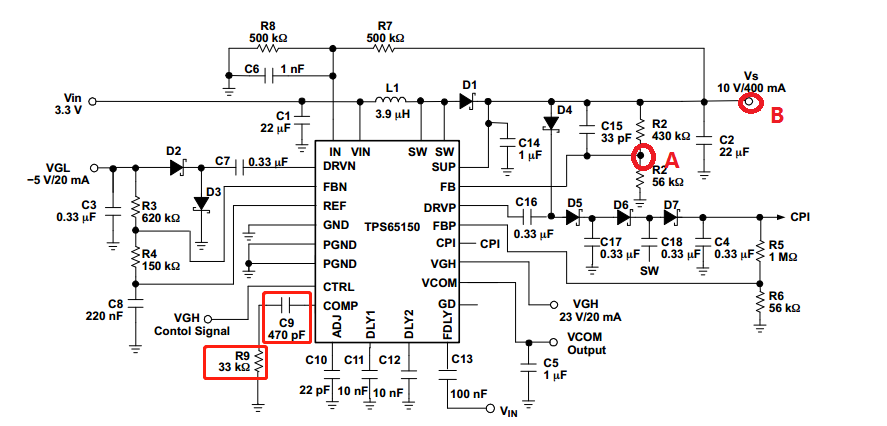

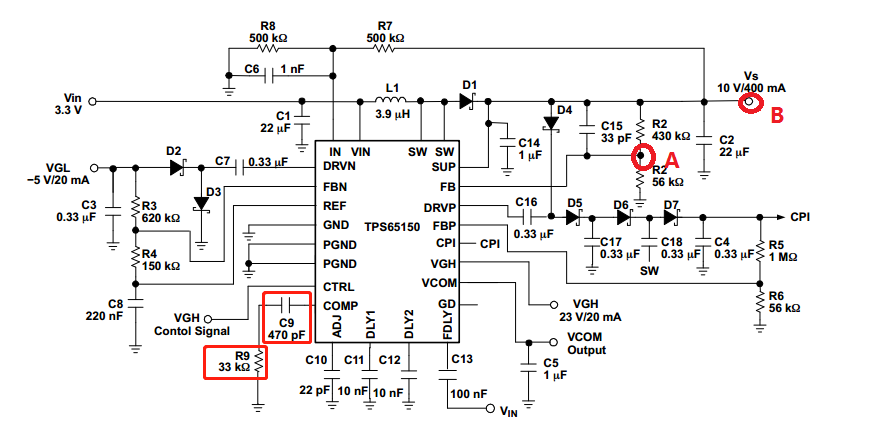

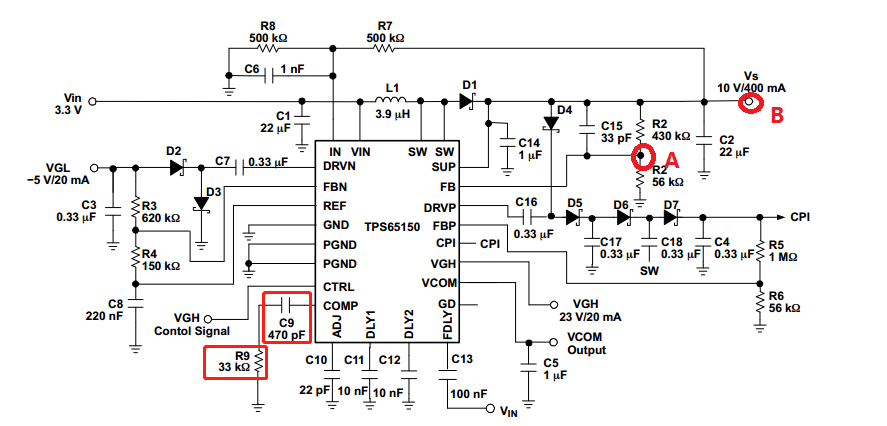

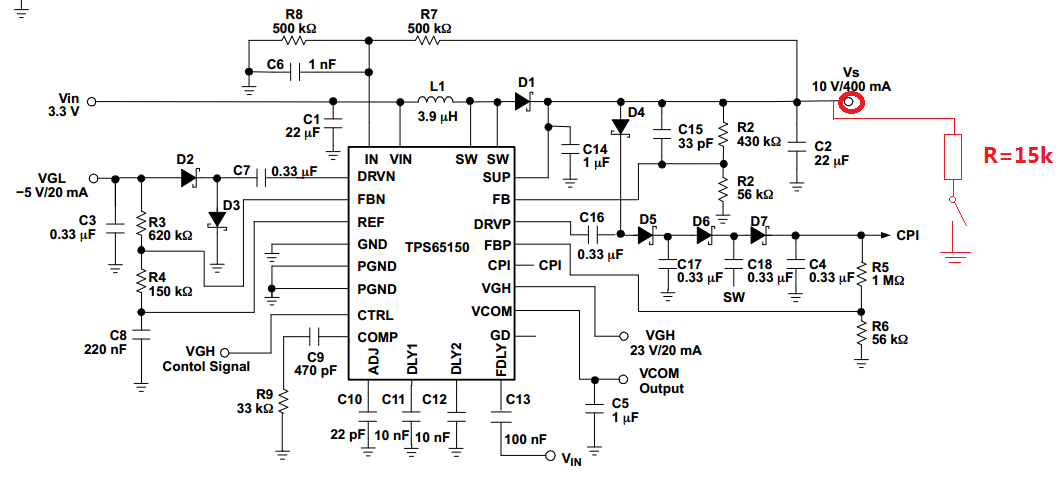

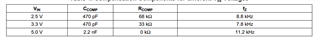

1.When VIN = 3.3 C9 = 2.2 nF R9 = 0 Ω, Ccomp & Rcomp choose like this, is OK? If this is the case, can the phase margin be greater than 45°? Friends who have actual tests can tell us. Thanks.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.