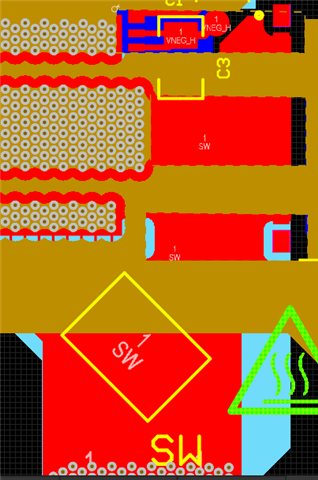

Figure 11.1 and 11.2 shows that switching node plane overlaps with power return plane. However, we know that switching node is a noisy plane and will probably make ground plane dirty below it. I have never overlapped my switching nodes in my designs so far. In the datasheet document it states that "Minimize overlap between the switch-node plane and other power and ground planes." From this quotation, I understand that overlapping has been done intentionally. The reason behind it could be that high frequency signals follows this overlapping path. If so, above what frequency does it start to hold true? If not, what is the reason behind, to some degree, overlapping switching node and ground plane ?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.