Hi team,

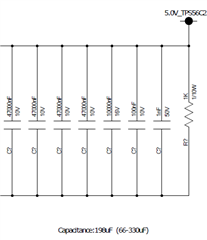

For 5.0V output with TPS56C230, the customer is using 4*47uF (10V rating) + 1*10uF (16V rating) + 1*100nF (10V rating) + 1*1nF (50V rating).

When it comes to 47uF capacitors, I expect its capacitance would decrease by half due to the voltage derating. Even though I consider the derating, the total output capacitance value meets the Cout.min requirement. In this case, do you expect any other problem with the capacitor derating ?