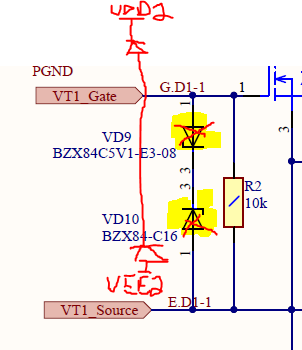

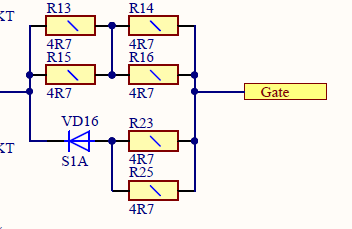

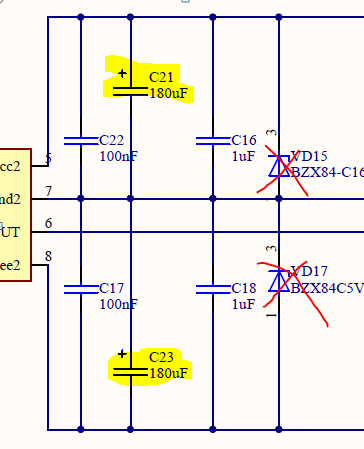

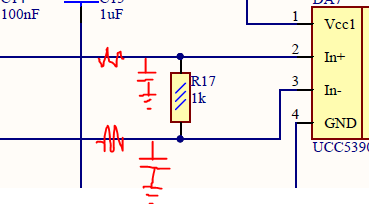

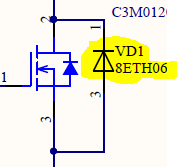

I have currently designed using ucc5390 an h bridge. here are the schematics and file.

i am confused about gate resistance value.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.