Other Parts Discussed in Thread: TPS62130A, , TPS53355

We have designed a server motherboard based on Intel's purely platform. The power controllers were used in the design are of TI and we took the help of webench for the reference design. We have been facing power issues while testing those boards. we are planning for the V2.0 release of the design. Before going for that step, we want our design to be reviewed by TI.

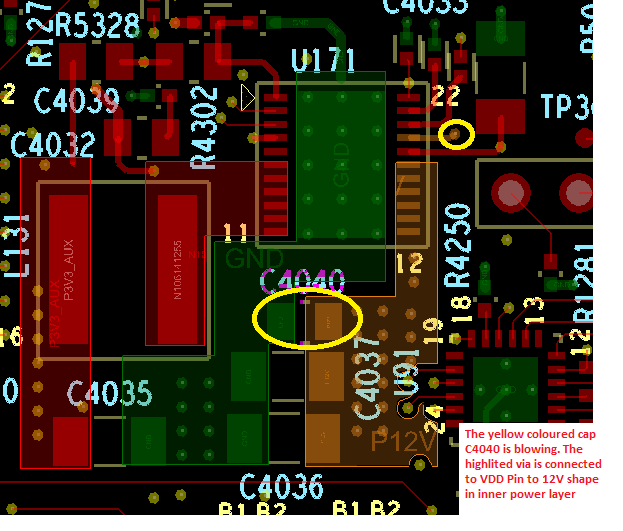

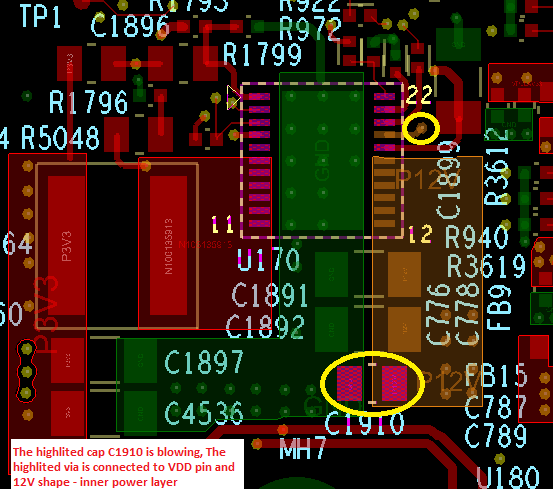

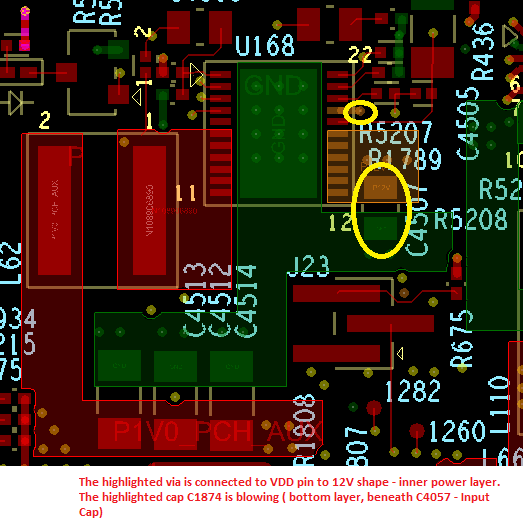

During the bring up some input capacitors were blown. (Refdes: C1874, C1910). - schematic is attached

Also please suggest the Input filter or EMI filter circuit as we did not implement such a filter circuit at any stage.

Please let me know if anything is needed