Other Parts Discussed in Thread: AM62P, SYSCONFIG, AM62P5-Q1, AM625, SK-AM62A-LP, AM620-Q1, AM625-Q1, AM623, AM625SIP,

Tool/software:

Hi TI Experts,

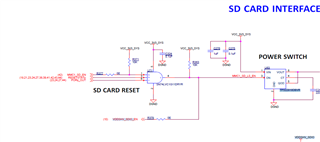

Is there a list of design recommendations or commonly observed errors for SD card Interface during Custom board hardware design?

Below are some common queries i have

1. Pullup recommendations

2. Power supply and Sequencing

3. Series resistor for SD card clock output from the processor

4. Power switch for SD card reset

,

,