Hi,

we´ve qot a custom board with DRA829V that uses SERDES3 as PCIe Root complex (1 lane).

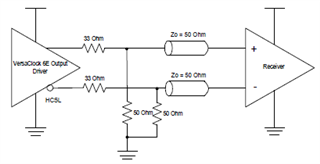

PCIE_REFCLK3P/N are driven by an external 100MHz HCSL clock (Output of a Renesas 5P49V60).

Following measurement shows the clock signal at processor side (after HCSL termination, differential).

After initialization of SERDES3, the signal gets even more distorted.

measurement differential:

measurement single ended PCIE_REFCLK3P:

measurement single ended PCIE_REFCLK3N:

Seems that the REFCLK pins are driving against the HCSL signal, although they should be configured as input, or what else could be the reason for this signal distortion?

Thanks for your support,

Peter