Dear Community,

I am contacting you because I have seen a failure we observed in one of our board.

The analysis brought us on a failure in the internal memory of the DSP in temperature preventing the SPI to be fully function in temperature.

In temperature (90°C) we are loosing the clearing of the INT of the MCP2515.

The investigation was the following:

With our firmware version, we found that we had this failure in temperature.

With a same firmware recompiled we still have the failure (not a compilation error).

We have added 3 NOP operation in a particular space of the memory map creating an offset in the SPI functions.

The board is working again with this new recompiled version.

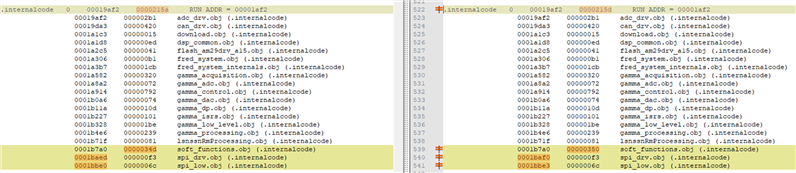

Below is the difference in the .map generated (Version with the bug in temperature in the left, Version recompiled with 3 NOP operation in the right)

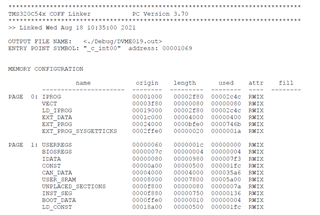

If I correctly understood, the moved part is in the LD_IPROG.

At the startup the LD_IPROG is copied to IPROG.

As the copy of LD_IPROG to IPROG is done once at the startup, the fact that the board is falling even when it was started up at 25°C and failure happen at 90°C, that mean IPROG might have some damage.

So, now how can I test the IPROG? Is it readable via JTAG XDS100v3? via Boundary Scan ?

Do you have any code to run a self-test on IPROG?

Can I run a feather code to read and write the IPROG sector (0x1000 to 0x3F80) ?

Thank you in advance,

Regards,