Other Parts Discussed in Thread: DP83869

Hello Sir,

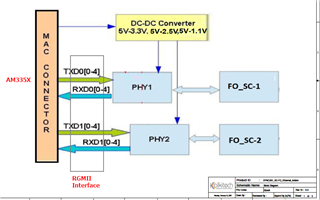

I was using dual "BCM54616S" Broadcom 10/100/1000 Phy chip with the copper interface with AM335x based controller.

Trying to migrate from Broadcom Copper PHY chip to a TI DP83869 Phy chip 100BASE-FX Fiber. For the same, I have made changes in U-Boot, Linux Kernel and DTB

We had issues in U-BOOT. The issues in U-Boot solved, when changed the Mask (DP83869_STRAP_OP_MODE_MASK) defined as follows. Now TFTP works well in U-BOOT

- #define DP83869_STRAP_OP_MODE_MASK GENMASK(2, 0)

+ #define DP83869_STRAP_OP_MODE_MASK GENMASK(11, 9)

- dp83869->mode = (u16) (val & DP83869_STRAP_OP_MODE_MASK);

+ dp83869->mode = (u16) ((val & DP83869_STRAP_OP_MODE_MASK) >> 9);

The mode set in strap is 'DP83869_RGMII_100_BASE'. When the proper mode got saved to variable 'dp83869->mode' , the issue solved.

--------------------------------------------------------------------------------

Currently we are facing issue in Linux Kernel (Kernel Version : 4.14.67). Network is not up with the new driver module (DP83869). Following error is coming in Boot-up log.

Configuring network interfaces... [ 9.118604] net eth0: initializing cpsw ver

sion 1.12 (0)

[ 9.127120] libphy: PHY 4a101000.mdio:02 not found

[ 9.131950] net eth0: phy "4a101000.mdio:02" not found on slave 0, err -19

[ 9.148662] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

PHY Address set in strap:

Eth0 : 10

Eth1 : 11

This is a similar issue as in following Question

e2e.ti.com/.../linux-am335x-ethernet-not-getting-up

I could find the following patch to resolve this issue. But unfortunately our mode is 'DUAL EMAC'

github.com/.../0001-cpsw-search-for-phy.patch

When applies the above patch, kernel panic is happening. Following is the boot-up log. I think the issue is happening when trying to configure second interface.

Configuring network interfaces... [ 22.024828] net eth0: initializing cpsw ver

sion 1.12 (0)

[ 22.073167] TI DP83869 4a101000.mdio:0a: attached PHY driver [TI DP83869] (mi

i_bus:phy_addr=4a101000.mdio:0a, irq=POLL)

[ 22.084071] Unable to handle kernel NULL pointer dereference at virtual addre

ss 00000000

[ 22.092202] pgd = c0004000

[ 22.104651] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

[ 22.111977] [00000000] *pgd=00000000

[ 22.132476] Internal error: Oops: 80000007 [#1] PREEMPT ARM

[ 22.138107] Modules linked in:

Appreciate if anyone can share patch/ solution to address this issue in AM335X DUAL MAC Mode.