Other Parts Discussed in Thread: AM3517

Hi team,

My customer is considering using TPS650732RSLR as PMIC for AM3505. I’ve got an inquiry on the powering up sequence, could you take a look below?

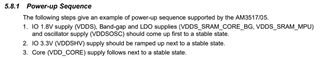

On the Application note (SLVA411), sequencing order is listed on the table 1. It has VDDSHV (3.3V) before VDDS_SRAM_CORE_BG and VDDS_SRAM_MPU.

On the other hand, in section 5.8.1 on the datasheet of AM3505 has example of powering up VDDS_SRAM_CORE_BG and VDDS_SRAM_MPU before the VDDSHV (3.3V).

Which one is correct? The datasheet says “an example”, so the sequencing order of VDDSHV and VDDS_SRAM doesn’t really matter?

Best regards,

Kurumi