Other Parts Discussed in Thread: DRA821U, DRA821,

Hi.

My customer is testing the TDA4 CAN on their PCB.

They already verified the CAN bus on the DRA821U of their pcb. It works well.

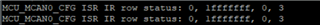

But, they migrate the code from DRA821U to TDA4. they found the CAN TX has no signal, meanwhile, CAN loop has no signal.

Any comments? (They are testing SDK8.2)

THanks.

BR Rio