Dear Sir,

There is "only one" OSPI interface (OSPI0) on AM64x platform and two CS are supported.

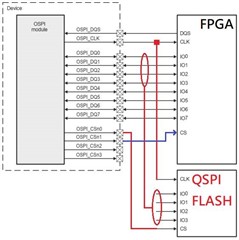

Customer uses OSPI to connect FPGA with high speed high frequency communication (OSPI PHY Mode DDR) and same OSPI with different CS is connected onto QSPI flash for booting and data storage.

The concern is the traces and capacitor loading on QSPI flash could affect the high speed communication between AM64x and FPGA.

Is there any recommendation or solution to reduce the affect from additional components on the same OSPI interface?

How to avoid the impact if the additional component cannot be removed? Will adding buffer or analog switch be helpful?

BR, Rich