- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

DRA821U: DRA821U: UDMA utilize OSPI access NorFlash configure read data length of every read command

Hello,

when I implemented DRA821 with Cypress NorFlash, we found following problem, I would appreciate it if you could help us with this problem, Thank you!

Fls failed to read&write with complete timeout issue. Fls config as below:

1. DRA821, NorFlash device is s28hs512t

2. Fls config as below:

CONST(struct Fls_ConfigType_s, FLS_CONFIG_DATA) FlsConfigSet =

{

.Fls_JobEndNotification = NULL_PTR,

.Fls_JobErrorNotification = NULL_PTR,

.maxReadNormalMode = 256U,

.maxWriteNormalMode = 256U,

.sectorList =

{

[0] =

{

.numberOfSectors = 256U,

.sectorPageSize = 256U,

.sectorSize = 262144U,

.sectorStartaddress = 1342177280U,

},

},

.dacEnable = FALSE,

.xipEnable = FALSE,

.ospiClkSpeed = 166666666U,

.dtrEnable = TRUE,

.phyEnable = FALSE,

};

More Information, 133MHz is ok, but not ok for 166MHz without any other difference.

Hello,

Which SDK release are you using?

And are you compiling a particular example and the only modification is the "dacEnable = FALSE"? Which example is this?

Regards,

Erick

SDK 8.0.

I am not using a particular example, dacEnable is highlighted because INDAC mode is not ok because dac mode is ok while INDAC mode is not.

Hello,

Let me try this combination on our J7200 EVM. We have an example application with in our MCUSW called fls_app_indac with these settings. I will try on SDK 8.0 and 8.2 to see if there is an issue with this config:

},

.dacEnable = FALSE,

.xipEnable = FALSE,

.ospiClkSpeed = 166666666U,

.dtrEnable = TRUE,

.phyEnable = FALSE,

};

Regards,

Erick

Zhongyi/Erick,

I asked Zhongyi to confirm in the other thread - is it intended to set phyEnable to FALSE for 166Mhz?

Jian

Hello,

I've tested the fls_app_indac example from SDK8.0 and SDK8.2, both are working fine.

They use the above configuration as default, so the configuration is seen to work correctly.

Can you please try running the fls_app_indac example on your board as well and see if it is passing correctly? Instructions are here:

The expected output from the app is also available in that documentation.

Regards,

Erick

Other test case:

we do the Fls initialization with following configuration data:

.Fls_JobEndNotification = NULL_PTR,

.Fls_JobErrorNotification = NULL_PTR,

.maxReadNormalMode = 1024U,

.maxWriteNormalMode = 256U,

.sectorList =

{

[0] =

{

.numberOfSectors = 256U,

.sectorPageSize = 256U,

.sectorSize = 262144U,

.sectorStartaddress = 1342177280U,

},

},

.dacEnable = TRUE,

.xipEnable = FALSE,

.ospiClkSpeed = 166666666U,

.dtrEnable = TRUE,

.phyEnable = TRUE,

after initialization, a read operation is done to finish OSPI tunning.

then, after some other codes, Fls_SwitchMode(FALSE,FALSE) is used to switch Fls mode into indac, here, the Fls erase and write operation not work.

Sun,

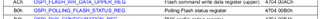

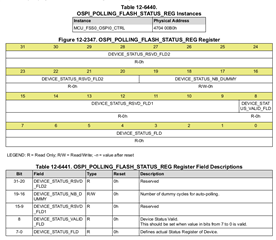

Can you please check this register

It contains a current known error with the MCAL Flash driver. There are bits corresponding to the dummy-cycles for auto-polling (19:16).

This field should be set to 8 for TDA4VM. For DRA821, it should be the same value, but we will need to verify the datasheet to be sure. Can you try setting this field to 8 if it has not been set already? Currently, the reset value is 0, so if you read 0 then it needs to be set to 8.

Please let me know if this helps.

Regards,

Erick

this register seems to be read only, cannot be modified by lauterbach debugger.

here, i'm doing a reading, but the read data is incorrect

/* get and check the first word and last word in the first page */

tmp0_u32 = *(uint32 *)MAIN_RESETLOG_BASE;

tmp1_u32 = *(uint32 *)((MAIN_RESETLOG_BASE + NOR_PAGE_SIZE) - 4uL);

Fls_SwitchMode(FALSE,FALSE);

if((tmp0_u32 != MAIN_RESETLOG_MAGIC_DATA) || (tmp1_u32 != MAIN_RESETLOG_MAGIC_DATA))

{

/* erase the log sector */

Fls_Erase((Fls_AddressType)(MAIN_RESETLOG_BASE - MEMLAY_NORFLASH_START), MAIN_RESETLOG_SIZE);

while(Fls_GetJobResult() == MEMIF_JOB_PENDING)

{

Fls_MainFunction();

}

}

emptyPageAddr_u32 = MAIN_RESETLOG_BASE;

/* search for a empty page */

while(emptyPageAddr_u32 < (MAIN_RESETLOG_BASE + MAIN_RESETLOG_SIZE))

{

Fls_Read((Fls_AddressType)(emptyPageAddr_u32 - MEMLAY_NORFLASH_START), LogDataR_au8, NOR_PAGE_SIZE);

while(Fls_GetJobResult() == MEMIF_JOB_PENDING)

{

Fls_MainFunction();

}

/* get and check the first word and last word of the page */

/* PRQA S 310 4 */

/* PRQA S 488 4 */

tmp0_u32 = *(uint32 *)LogDataR_au8;

tmp1_u32 = *(uint32 *)(LogDataR_au8 + (NOR_PAGE_SIZE - 4uL));

if((tmp0_u32 == 0xFFFFFFFFuL) && (tmp1_u32 == 0xFFFFFFFFuL))

{

break;

}

emptyPageAddr_u32 += NOR_PAGE_SIZE;

}

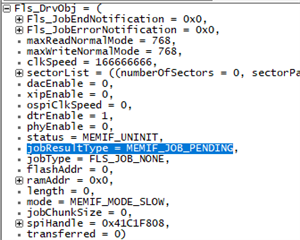

I did some tests based on our Fls configuration and OSPI clock, see test code and configuration below.

case1: select MCU_PLL1_HSDIVOUT4 133MHz as OSPI clock, both the Fls initializations are finished successfully.

case2: select MCU_PLL2_HSDIVOUT4 166MHz as OSPI clock, the first Fls initialization finished successfully, during the second one, the Nor_xspiReadId() is incorrect, first manufacturerId byte is incorrect.

tested code: a simulation process of our software:

1 clock selection for OSPI, MCU_PLL2_HSDIVOUT4 is 166MHz, MCU_PLL1_HSDIVOUT4 is 133MHz.

2 firstly Fls initialized with FlsConfigSet, DAC, PHY enabled

3 a tuning is done

4 100ms delay

5 Fls initialized again with new configuration data FlsConfigSet1, INDAC, PHY disable

/* clock selection for OSPI */

Target_OspiClkInit();

Fls_Init(NULL_PTR);

(void)Nor_spiPhyTune(Fls_DrvObj.spiHandle, NOR_TUNING_DATA_OFFSET);

Main_DelayMs(100uL);

/* code will not reach here if no error */

Fls_Init(&FlsConfigSet1);

CONST(struct Fls_ConfigType_s, FLS_CONFIG_DATA) FlsConfigSet =

{

.Fls_JobEndNotification = NULL_PTR,

.Fls_JobErrorNotification = NULL_PTR,

.maxReadNormalMode = 768U,

.maxWriteNormalMode = 768U,

.sectorList =

{

[0] =

{

.numberOfSectors = 256U,

.sectorPageSize = 256U,

.sectorSize = 262144U,

.sectorStartaddress = 1342177280U,

},

},

.dacEnable = TRUE,

.xipEnable = FALSE,

.ospiClkSpeed = 166666666U,

.dtrEnable = TRUE,

.phyEnable = TRUE,

};

CONST(struct Fls_ConfigType_s, FLS_CONFIG_DATA) FlsConfigSet1 =

{

.Fls_JobEndNotification = NULL_PTR,

.Fls_JobErrorNotification = NULL_PTR,

.maxReadNormalMode = 768U,

.maxWriteNormalMode = 768U,

.sectorList =

{

[0] =

{

.numberOfSectors = 256U,

.sectorPageSize = 256U,

.sectorSize = 262144U,

.sectorStartaddress = 1342177280U,

},

},

.dacEnable = FALSE,

.xipEnable = FALSE,

.ospiClkSpeed = 166666666U,

.dtrEnable = TRUE,

.phyEnable = FALSE,

};

this register seems to be read only, cannot be modified by lauterbach debugger.

It is accessible on CCS debugger, I wonder why Lauterbach does not allow modification. Please try modifying it after boot, before launching the application. If debugger does not allow, can you access register directly through your application code? Address should be 0x470400B0.

Regards,

Erick

I have tested the setting in application, but for the second Fls_Init(), initialization still failed.

Hello,

Not sure if this makes a difference, but I usually make the update to the register after Fls_init(). Could you make sure the register write is after?

But I don't think this would be the issue now, once it is set it should stay set.

Have you been able to run our example as I mentioned above?

Can you please try running the fls_app_indac example on your board as well and see if it is passing correctly? Instructions are here:

This will help confirm there is no HW issue.

Regards,

Erick