Dear all,

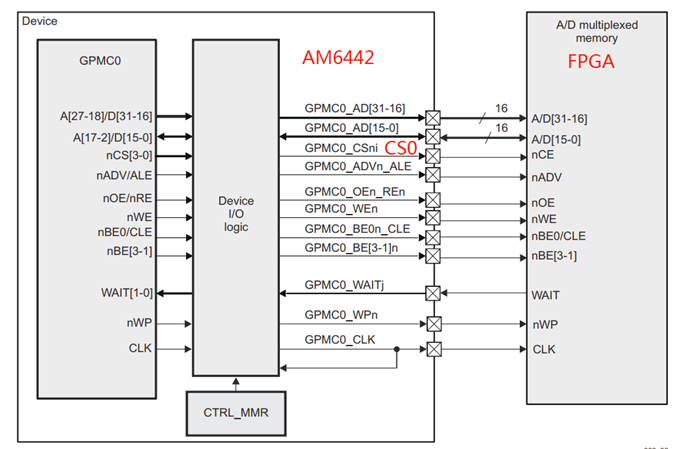

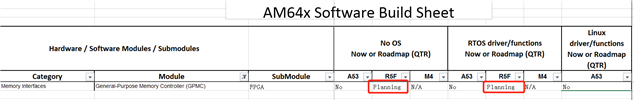

we use AM6442 GPMC access FPGA by 32-bit Multiplexed Address/Data synchronize NOR type without waitpin monitor.

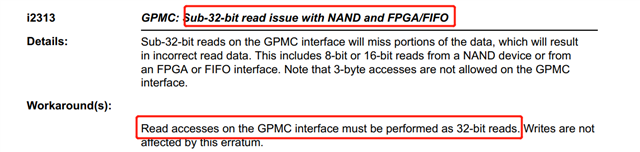

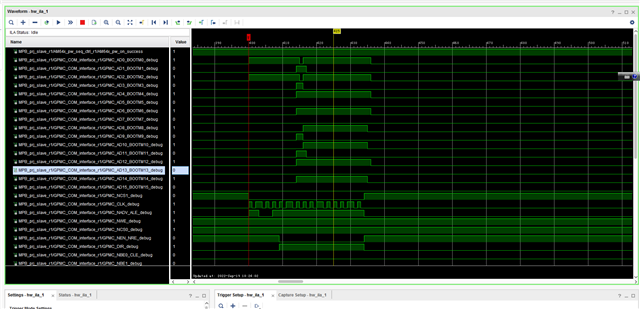

But we always read 0 no matter FPGA gpmc region value is 0 or not.below is waveform.

AM6442 ver is PG1.0 we've used.Is this phenomenon right?

thanks,

jimin.li