Dear TI team,

I would like to know the possibility to wake up SoC from DeepSleep power mode through CAN RX?

I am using CAN Trcv TJA1043 which can provide also INH pin as high-level in STBY and Normal modes, and as low-level in Sleep mode.

INH pin is connected to PMIC, so if INH pin goes low, PMIC will turn off SoC.

Therefore waking up SoC from INH is not possible since it is edge triggered and this means PMIC will turn off SoC.

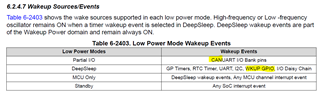

As per the below table from AM62x TRM, CAN pins are not a wakeup source in DeepSleep. Therefore I was wondering if there is an application note about this case of sleep/wakeup mechanism.

Thanks and regards,

Marwan