Other Parts Discussed in Thread: DRA821, , TDA4VH, DRA829

Are there any tools available for printing ALE for the different ethernet applications with enet LLD, ethfw and Native Linux Driver?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

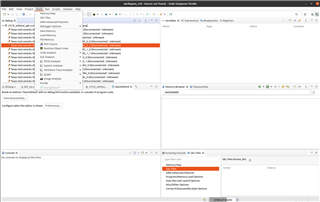

MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: -------CPSW2G ALE TABLE---------------------- MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 0 - VLAN MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 2 MAIN_Cortex_R5_0_1: GEL Output: VLAN_ID = 0 MAIN_Cortex_R5_0_1: GEL Output: FORCE_UNTAG_EG = 3 MAIN_Cortex_R5_0_1: GEL Output: REG_MCAST_FLOOD = 272 MAIN_Cortex_R5_0_1: GEL Output: UNREG_MCAST_FLOOD = 0 MAIN_Cortex_R5_0_1: GEL Output: VLAN_MEMBER_LIST = 3 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 1 - Unicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_NUMBER = 0 MAIN_Cortex_R5_0_1: GEL Output: BLOCK = 0 MAIN_Cortex_R5_0_1: GEL Output: SECURE = 1 MAIN_Cortex_R5_0_1: GEL Output: UNICAST_TYPE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: UNICAST_ADDR = 0x00002476 0x25934C39 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 2 - VLAN/Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000003 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 3 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 3 MAIN_Cortex_R5_0_1: GEL Output: VLAN_ID = 0 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x0000FFFF 0xFFFFFFFF MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 3 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00003333 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 4 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000100 0x5E000001 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 5 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000180 0xC2000000 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 6 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000180 0xC2000003 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 7 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000180 0xC200000E MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 8 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00003333 0xFF934C39 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 9 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00003333 0x000000FB MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 10 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00003333 0x00010003 MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 11 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000100 0x5E0000FC MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: Entry 12 - Multicast MAIN_Cortex_R5_0_1: GEL Output: --------------------------------------------- MAIN_Cortex_R5_0_1: GEL Output: PORT_MASK = 0x00000001 MAIN_Cortex_R5_0_1: GEL Output: SUPER = 0 MAIN_Cortex_R5_0_1: GEL Output: MCAST_FWD_STATE = 0 MAIN_Cortex_R5_0_1: GEL Output: ENTRY_TYPE = 1 MAIN_Cortex_R5_0_1: GEL Output: MULTICAST_ADDR = 0x00000100 0x5E0000FB MAIN_Cortex_R5_0_1: GEL Output: Completed analysis of 64 ALE entries

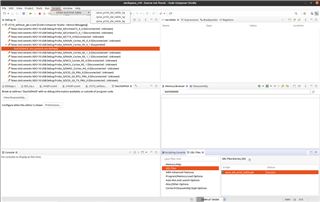

0: Vlanid: 012c, UTagged: 1ff, Mult: 1ff, UMult: 0, Member: 1ff RAW:[0 212c1ff1 ff0001ff]

1: Vlanid: 0000, UTagged: 13, Mult: 13, UMult: 13, Member: 13 RAW:[0 20000130 13013013]

2: Vlanid: 0001, UTagged: 1ed, Mult: 1ed, UMult: 0, Member: 1ed RAW:[0 20011ed1 ed0001ed]

3: Address: ffffffffffff, Member:1ff Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[7fc 1000ffff ffffffff]

4: Address: 70ff761d92c3, Port: 000 Se=1 Bl=0 TOUCH=0 AGE=0 TRUNK=0 RAW:[1 100070ff 761d92c3]

5: EtherType: 0806 RAW:[1 20000000 00000806]

6: Address: 70ff761d92c2, Port: 000 Se=0 Bl=0 TOUCH=0 AGE=0 TRUNK=0 RAW:[0 100070ff 761d92c2]

7: Address: 333300000001, Member:001 Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[4 10003333 00000001]

8: Address: 70ff761d92c1, Port: 000 Se=1 Bl=0 TOUCH=0 AGE=0 TRUNK=0 RAW:[1 100070ff 761d92c1]

9: Address: 01005e000001, Member:001 Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[4 10000100 5e000001]

10: Address: 3333ff1d92c2, Member:001 Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[4 10003333 ff1d92c2]

11: Address: 3333000000fb, Member:1ed Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[7b4 10003333 000000fb]

12: Address: 0180c2000000, Member:001 Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[4 10000180 c2000000]

13: Address: 0180c2000003, Member:001 Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[4 10000180 c2000003]

14: Address: 333300010003, Member:1ed Su=0 FWDSTLVL=0 IGNMBITS=0 RAW:[7b4 10003333 00010003]

1009 Free Entries

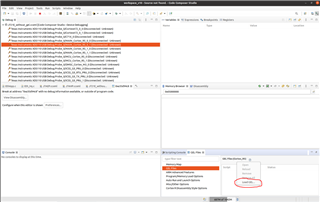

0: POLICER_DST_MAC,ALE Index: 3

0: POLICER_ETHERTYPE,ALE Index: 5

0: POLICER_THREAD,THREAD ID:4

0: POLICER_STATS: Hit: 0, RedHit: 0, YellowHit: 0

1: POLICER_DST_MAC,ALE Index: 6

1: POLICER_THREAD,THREAD ID:1

1: POLICER_STATS: Hit: 0, RedHit: 0, YellowHit: 0

2: POLICER_PORT, PORT_NUM: 1 ISTRUNK:0

2: POLICER_THREAD,THREAD ID:0

2: POLICER_STATS: Hit: 0, RedHit: 0, YellowHit: 0

3: POLICER_DST_MAC,ALE Index: 11

3: POLICER_THREAD,THREAD ID:1

3: POLICER_STATS: Hit: 1, RedHit: 0, YellowHit: 0

4: POLICER_DST_MAC,ALE Index: 14

4: POLICER_THREAD,THREAD ID:1

4: POLICER_STATS: Hit: 1, RedHit: 0, YellowHit: 0

91 Free Entriesroot@j7200-evm:~# switch-config --ndev eth1 -d K3 cpsw dump version (1) len(11704) ALE table dump ents(512): 0 : type: vlan , vid = 0, untag_force = 0x7, reg_mcast = 0x1, unreg_mcast = 0x0, member_list = 0x7 1 : type: mcast, addr = 01:00:5e:00:00:01, mcast_state = f, no super, port_mask = 0x1 2 : type: ucast, vid = 1, addr = 70:ff:76:1d:a0:7b, ucast_type = persistant, port_num = 0x0, Secure, Blocked 3 : type: mcast, vid = 1, addr = ff:ff:ff:ff:ff:ff, mcast_state = f, no super, port_mask = 0x7 4 : type: mcast, addr = 01:80:c2:00:00:00, mcast_state = f, no super, port_mask = 0x1 5 : type: mcast, addr = 01:80:c2:00:00:03, mcast_state = f, no super, port_mask = 0x1 6 : type: mcast, addr = 01:80:c2:00:00:0e, mcast_state = f, no super, port_mask = 0x1 7 : type: ucast, vid = 1, addr = 70:ff:76:1d:a0:7c, ucast_type = persistant, port_num = 0x0, Secure, Blocked 8 : type: mcast, addr = 33:33:00:00:00:01, mcast_state = f, no super, port_mask = 0x1 9 : type: mcast, addr = 33:33:ff:1d:a0:7c, mcast_state = f, no super, port_mask = 0x1 12 : type: vlan , vid = 1, untag_force = 0x6, reg_mcast = 0x0, unreg_mcast = 0x0, member_list = 0x6 33 : type: ucast, vid = 1, addr = 24:76:25:93:4c:39, ucast_type = touched , port_num = 0x1 50 : type: ucast, vid = 1, addr = 00:68:eb:b6:6e:6e, ucast_type = untouched , port_num = 0x2

Regards,

Tanmay