Hi,

My customer built proto-type boards with SR2.0 devices (AM6412BSCGHAALV).

But these boards showed a boot issue from micro SD card.

21 boards out of 60 boards showed the same behavior.

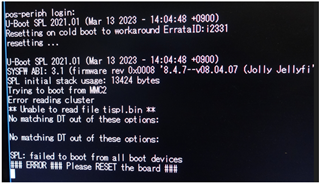

Boot sequence stops with below error.

Please note that the same error happens if no image is written in SD card, but the customer confirmed the image was properly written.

Remaining boards (39 out of 60) also showed the same error, but they can boot-up after ~10 times of power cycles.

After the first SD card boot, the ROM image is loaded on eMMC. Then the system boots up from eMMC after that.

No issue observed with eMMC boot, so the issue is related to SD card boot.

And even among the same SD card part#, some cards passed and some cards failed.

The customer did not observed the issue with SR1.0 samples (XAM6442) and they did not change PCB around the device for SR2.0.

It is very critical for customer development.

Please provide how to investigate the issue.

Thanks and regards,

Koichiro Tashiro

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.