Other Parts Discussed in Thread: SYSCONFIG

Hi,

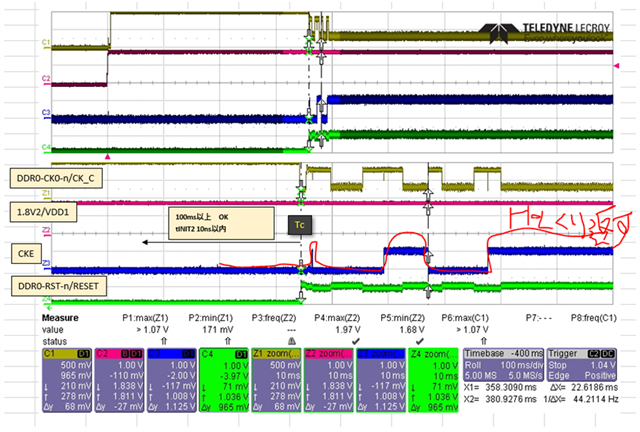

My customer reported LPDDR4 access failure with SR2.0 silicon.

They used SR1.0 silicon before and there were no failure with SR1.0.

The customer used sysconfig sysconfig v0.08.08.

Memory test was done with;

https://linux.die.net/man/8/memtester

and below command.

root@am64xx-evm:~# ./memtester 256M 5

Q1) Are there any LPDDR4 configuration changes are required between SR1.0 and SR2.0?

If so, which configuration?

Q2) They tried to update sysconfig v0.09.08 and 1333 configuration are passed.

But 1600 configuration still failed on SR2.0.

Below excel file shows how to configure sysconfig for 1600.

Could you check it and let me know if anything is wrong?

LPDDR4 configuration.xlsx

FYI, for 1333 configuration, only "FSP2 Frequency (MHz)" is changed to "666.7".

Q3) In sysconfig v0.08.08, selected Device name was "AM64x_beta".

Now it is "AM64x" in v0.09.08. Are there any changes done between these versions?

Thanks and regards,

Koichiro Tashiro