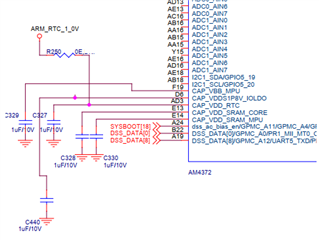

Part Number: AM4372

Hi,

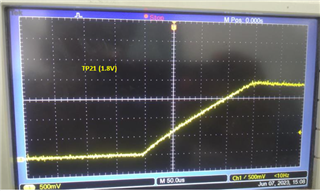

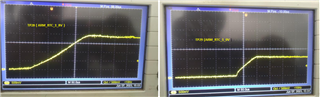

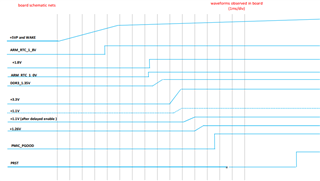

We have AM4372 based PCB which is designed to follow normal power-up sequence as described in sec. 5.12.1.2 of datasheet.

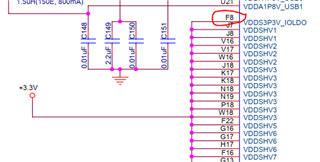

In the board, pin#F8 (VDDS3P3V_IOLDO) is connected to 3.3V supply, but pin#D6 (CAP_VDDS1P8V_IOLDO) is not connected to VDDS or VDDS_CLOCKOUT or any other load in the board.

VDDS , VDDS_CLOCKOUT are powered from a separate 1.8V supply

We are using LTC3676-1 as the PMIC.

Is it OK to connect VDDS3P3V_IOLDO to 3.3V but powering VDDS and VDDS_CLOCKOUT from a separate source in normal power-up sequence ?

Regards,

Thomas Joseph