Hi TI expert

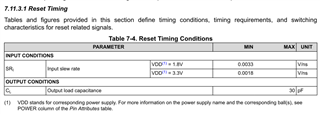

For Reset input signal there are SRi parameter listed in Datasheet, but i feel confuse about which edge SRi should be monitored and why?

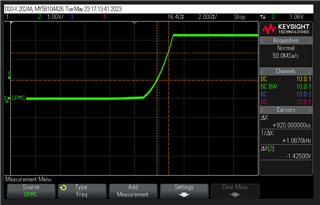

For first power on stage, Reset pin 's rising time can't meet SRi > 3.3E+6 V/s spec, any risk?

BR Jingcheng