Hi,

When we send data from R5F core to A72 through shared memory, there is a situation of inconsistent data acceptance. For example, R5F sends data 3 times, 1, 2, and 3 respectively. However, A72 may only receive 1, 2, 2. See the following figure for details of the code:

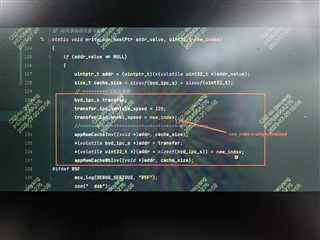

The R5F code is as follows:

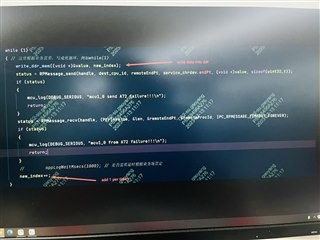

A72 Acceptances are as follows:

A72 relevant codes are as follows:

What is the cause of this problem? How should it be resolved? Thank you!

Regards,

Kong