Other Parts Discussed in Thread: PCM3168A, LM5060

Hi,

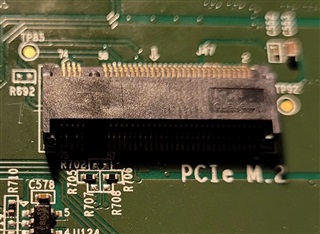

I have a J721EXSOM and it looks like the M.2 socket is not enabled in the latest SDK 09.00.01.03 .

lspci doesn't return anything and:

dmesg | grep pcie

[ 6.212400] j721e-pcie-host 2910000.pcie: host bridge /bus@100000/pcie@2910000 ranges:

[ 6.237965] j721e-pcie-host 2910000.pcie: IO 0x0018001000..0x0018010fff -> 0x0018001000

[ 6.248375] j721e-pcie-host 2910000.pcie: MEM 0x0018011000..0x001fffffff -> 0x0018011000

[ 6.257924] j721e-pcie-host 2910000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000

[ 6.393139] j721e-pcie-host 2910000.pcie: Failed to init phy

[ 6.399991] j721e-pcie-host: probe of 2910000.pcie failed with error -110

[ 6.443755] j721e-pcie-host 2920000.pcie: host bridge /bus@100000/pcie@2920000 ranges:

[ 6.601554] Modules linked in: ti_k3_r5_remoteproc(+) videobuf2_dma_sg videobuf2_dma_contig cdns_mhdp8546(+) v4l2_mem2mem videobuf2_memops videobuf2_v4l2 v4l2_async videobuf2_common tidss drm_display_helper drm_dma_helper drm_kms_helper cfbfillrect ti_k3_dsp_remoteproc(+) videodev syscopyarea pruss virtio_rpmsg_bus ti_am335x_tscadc cfbimgblt pvrsrvkm(O) sysfillrect rpmsg_ns mc sysimgblt ti_j721e_ufs cdns_dphy_rx sa2ul fb_sys_fops ti_k3_common pci_j721e_host(+) cfbcopyarea pci_j721e cdns3_ti pcie_cadence_host snd_soc_davinci_mcasp pcie_cadence snd_soc_ti_udma snd_soc_ti_edma snd_soc_ti_sdma m_can_platform m_can snd_soc_pcm3168a_i2c can_dev snd_soc_pcm3168a rti_wdt ina2xx optee_rng rng_core cryptodev(O) fuse drm drm_panel_orientation_quirks ipv6

[ 6.696838] j721e-pcie-host 2920000.pcie: IO 0x4400001000..0x4400010fff -> 0x0000001000

[ 6.776994] j721e-pcie-host 2920000.pcie: MEM 0x4400011000..0x4407ffffff -> 0x0000011000

[ 6.837014] j721e-pcie-host 2920000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000

[ 7.271078] j721e-pcie-host 2920000.pcie: Failed to init phy

[ 7.398523] j721e-pcie-host: probe of 2920000.pcie failed with error -110

[ 20.335802] platform 2900000.pcie: deferred probe pending

Does platform '2900000.pcie: deferred probe pending' correspond to the M.2 slot ?