- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

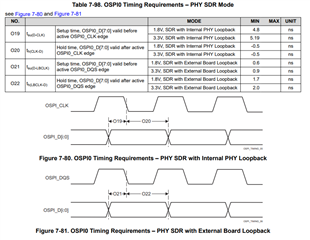

My customer wants to confirm OSPI timing requirements for PHY SDR mode without data training.

Below is Datasheet Table 7-98, Figure 7-80 and 7-81.

Q1) These description means the "active OSPI0_CLK edge" is "falling edge", correct?

Q2) Below waveform is actual OSPI0_CLK and D0 on the customer's board.

Setup and hold should be measured at the dotted line (start of clock falling edge)?

Thanks and regards,

Koichiro Tashiro

Hello Koichiro Tashiro

Thank you.

Q2) Below waveform is actual OSPI0_CLK and D0 on the customer's board.

Setup and hold should be measured at the dotted line (start of clock falling edge)?

Please provide additional details on the setup - EVM or custom board and the location of the measurements.

Regards,

Sreenivasa

Hi Sreenivasa,

Please provide additional details on the setup - EVM or custom board and the location of the measurements.

The waveform was monitored on a custom board and probe location is near Flash memory.

OSPI is internal PHY loopback mode.

Thanks and regards,

Koichiro Tashiro

Hello Koichiro Tashiro

Thank you for the inputs.

Do you have series resistors or parallel pullups or any filter cap on the interface signals?

Is the clock connection point to point?

Regards,

Sreenivasa

Hello Koichiro Tashiro

Refer below additional inputs i received from one of the expert

Is the customer sure the waveform they captured represents read data?

We typically use the mid-supply point on the clock for timing.

I only read the original post provided below and just realized they already said they were using Internal PHY Loopback mode.

What clock frequency are they trying to use? It appears to be near the max frequency based on the rise/fall times relative to the clock period, but I’m not able to tell since there is no time scale on the scope capture.

What are their PCB delays? They must also consider the impact of PCB delays if trying to determine timing margin for AM64x when measuring the signal timing relationship near the OSPI device. The timing requirements in the datasheet are only applicable when measured at the AM64x pins.

Could you please add your thoughts and also provide additional details.

Regards,

Sreenivasa

Hi Sreenivasa,

I will check for the details you asked, but could you first provide an answer to the customer's original question below?

This is "Yes" or "No" type question.

Setup and hold should be measured at the dotted line (start of clock falling edge)?

Please note that the waveform is shown just for reference purpose.

The customer understood the datasheet timing is defined at AM64x pin. He wants to know where are the setup and the hold period.

Thanks and regards,

Koichiro Tashiro

Hello Koichiro Tashiro

Thank you.

Setup and hold should be measured at the dotted line (start of clock falling edge)?Please note that the waveform is shown just for reference purpose.

We typically use the mid-supply point on the clock for timing.

Regards,

Sreenivasa

Hi Sreenivasa,

What clock frequency are they trying to use?

The clock is 125MHz.

I will send you the customer schematics offline to answer other questions.

Thanks and regards,

Koichiro Tashiro

Hello Koichiro Tashiro

Thank you.

I will review the inputs and come back.

Regards,

Sreenivasa

Hello Koichiro Tashiro

Please refer below inputs i received from the expert.

Their question seemed to be related to our capture timing. We need them to confirm the waveform provided represents read data and they need to provide PCB delays before we can determine how much margin is being provided for host data capture. Are they planning to answer these questions?

Regards,

Sreenivasa