Part Number: AM69

Other Parts Discussed in Thread: CLOCKTREETOOL,

Our customer wants to know more about reference clocks for PCIe.

Q1) Is SERDESn_REFCLK_x an input/output or input only?

In datasheet:

Each PCIe subsystem has a differential reference clock output (PCIE_REFCLKn_N_OUT, PCIE_REFCLKn_P_OUT).

Each SERDES module has a differential reference clock input/output (SERDESn_REFCLK_N, SERDESn_REFCLK_P).

AM69x Processors, Silicon Revision 1.0 datasheet (Rev. A)

Table 6-88. PCIE Signal Descriptions

Table 6-89. SERDES0 Signal Descriptions

Table 6-90. SERDES1 Signal Descriptions

Table 6-91. SERDES2 Signal Descriptions

Table 6-92. SERDES4 Signal Descriptions

In TRM:

Each SERDES module has a differential reference clock output (PCIE_REFCLK_P_OUT, PCIE_REFCLK_N_OUT) and a differential reference clock input (SERDES_REFCLK_P, SERDES_REFCLK_N).

J784S4/TDA4AP/TDA4VP/TDA4AH/TDA4VH/AM69A Processors Technical Reference Manual (Rev. C)

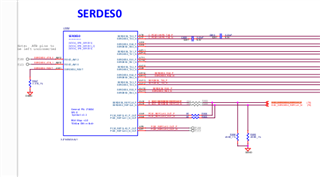

Figure 12-126. SerDes Environment

Table 12-204. SerDes Input/Output Description

Q2) Can SERDESn_REFCLK_x be used as a reference clock for SerDes?

In TRM, it seems that the internal reference clock for SerDes can only be selected from internal clock sources.

J784S4/TDA4AP/TDA4VP/TDA4AH/TDA4VH/AM69A Processors Technical Reference Manual (Rev. C)

Table 12-203. SerDes Internal Reference Clock Selection

Q3) Are the selectable clock sources for PCIE_REFCLKn_x_OUT as shown in Table 12-202 on TRM?

J784S4/TDA4AP/TDA4VP/TDA4AH/TDA4VH/AM69A Processors Technical Reference Manual (Rev. C)

Table 12-202. SerDes ACSPCIe Reference Clock Selection

Q4) If an internal clock source is used for the reference clock for SerDes, can SERDESn_REFCLK_x be unused?

Q5) If SERDESn_REFCLK_x is unused, how is it recommended to be connected? Can it be left unconnected?

Q6) If an internal clock source is used for the reference clock for SerDes, can PCIE_REFCLKn_x_OUT be used as reference clock output for an external PCIe device?

Q7) If so, should "MAIN_PLL2_HSDIV4_CLKOUT" be selected for both PCIE_REFCLKn_x_OUT and the reference clock for SerDes?

Q8) Does PSDK Linux support the configuration of selecting an internal clock source for reference clock for SerDes and selecting the internal clock source for PCIE_REFCLKn_x_OUT?

Best regards,

Daisuke