Hello,

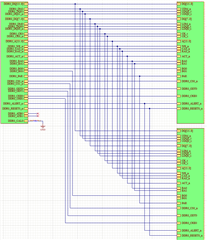

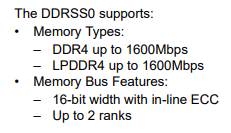

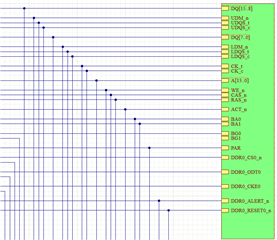

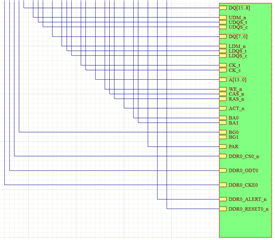

Referring to the AM620x DDR design guide https://www.ti.com/lit/an/sprad06/sprad06.pdf I come across this screenshot showing one 16 bit DDR connection to the microprocessor. In it, the DDR0_BG1, DDR0_CS1, DDR0_ODT1, and DDR0_CKE1 pins are No Connects.

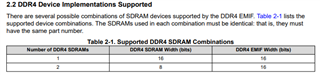

Does TI see a reason why there cant be a second DDR interface connected to those No Connect lines mentioned above? All other signal lines shown would be shared between the two devices.