Hello,

Let me confirm meaning of GPIO2_12 and 2_13 of ICE board version 2.1.

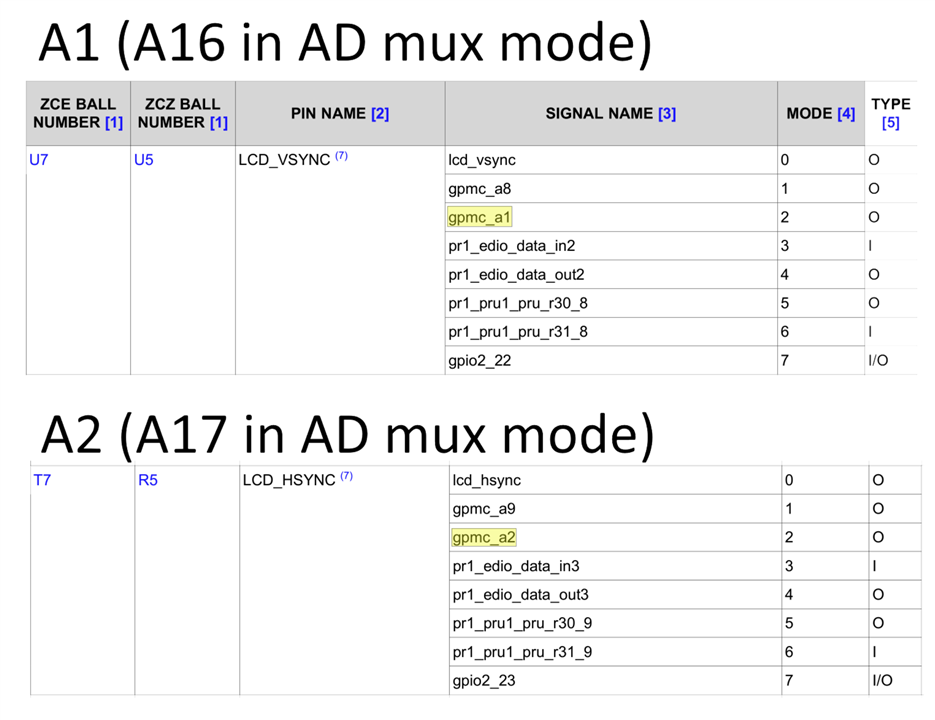

According to following user's guide, it seems that above two are for GPMC_A18 and A19 of NOR flash.

https://www.ti.com/jp/lit/ug/spruip3/spruip3.pdf

However, it seems that these are set as GPIO not GPMC.

Then I have following questions ?

Q1. Is my above understanding that signal "gpio2_12" and "gpio2_13" are set as GPIO correct ?

Q2. If so, is there any information how you control these gpios as address function of GPMC ?

BR,

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.