Hi Experts,

Our equipment uses TMS320VC5509A and we are experiencing problems with this equipment.

The problem is that the McBSP output signal has jitter.

As an investigation, I configured the CLKOUT pin to output CPU CLOCK.

As a result, the CPU CLOCK was also experiencing jitter.

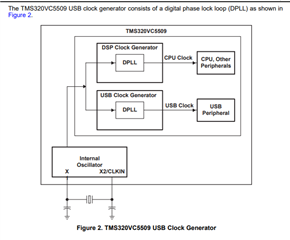

The clock input to the X2 pin(approximately 24MHz) is multiplied by the internal clock generator PLL and used as the CPU CLOCK.

As a result of our investigation, we have found the following, but we do not know why this phenomenon occurs.

・Changing the PLL multiplier will change the amount of jitter.(Jitter is larger at x3 than at x4)

・Comparing the idle state and the operating state (where software processing is heavy), the jitter is larger in the operating state.

What are the possible causes of this phenomenon?

We would like to provide specific measurement waveforms on an individual basis.

Additional information

・Power supply voltage is DVDD:3.3V, CVDD:1.6V

・We verified that there is no jitter on the clock input using an oscilloscope and FET probe.

Best regards,