Other Parts Discussed in Thread: SYSBIOS,

Hi, TI experts,

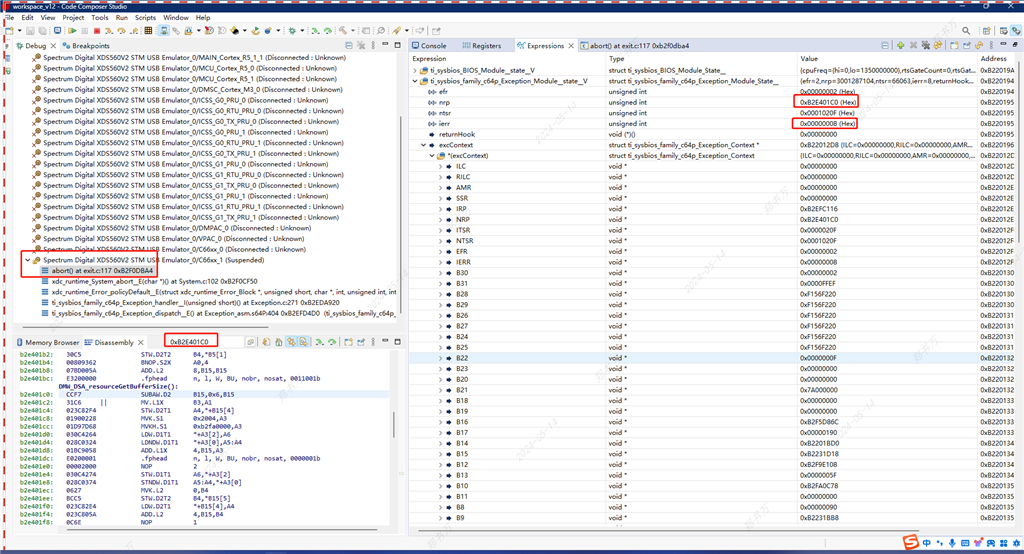

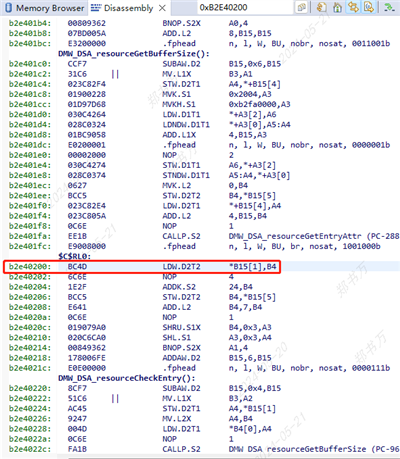

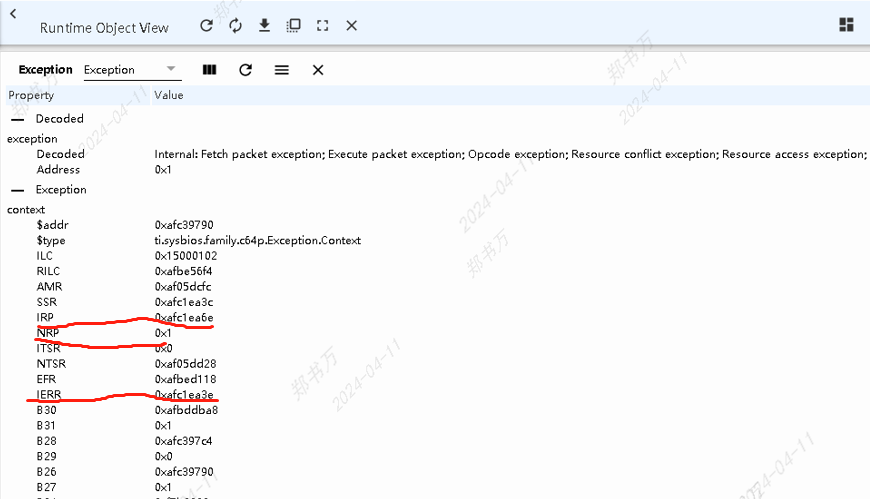

1. TDA4 device DSP C660 aborted and opcode exception,show as follows:

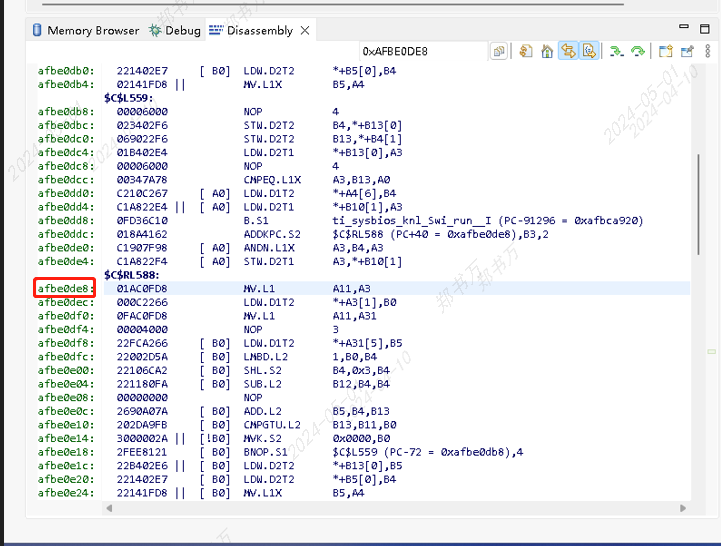

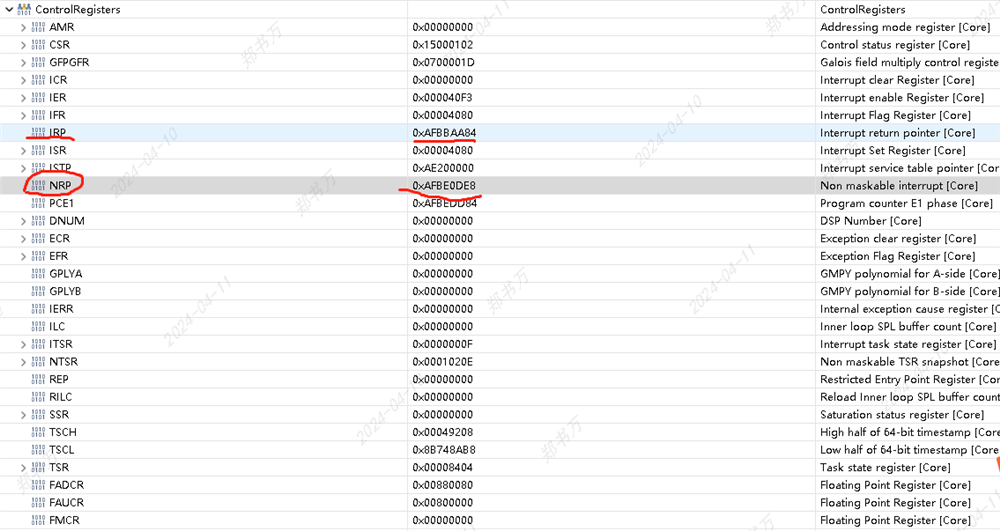

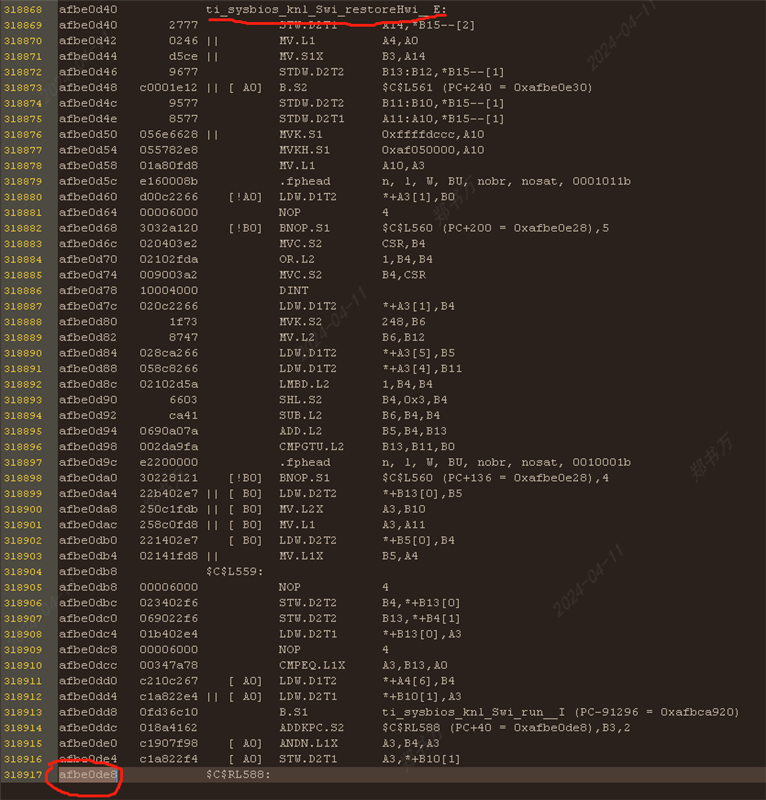

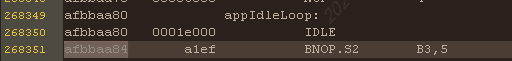

IRP:0xAFBBAA84(IDLE Task);NRP:0xAFBE0DE8(ti_sysbios_knl_Swi_restoreHwi__E);IERR:0x8(opcode exception)

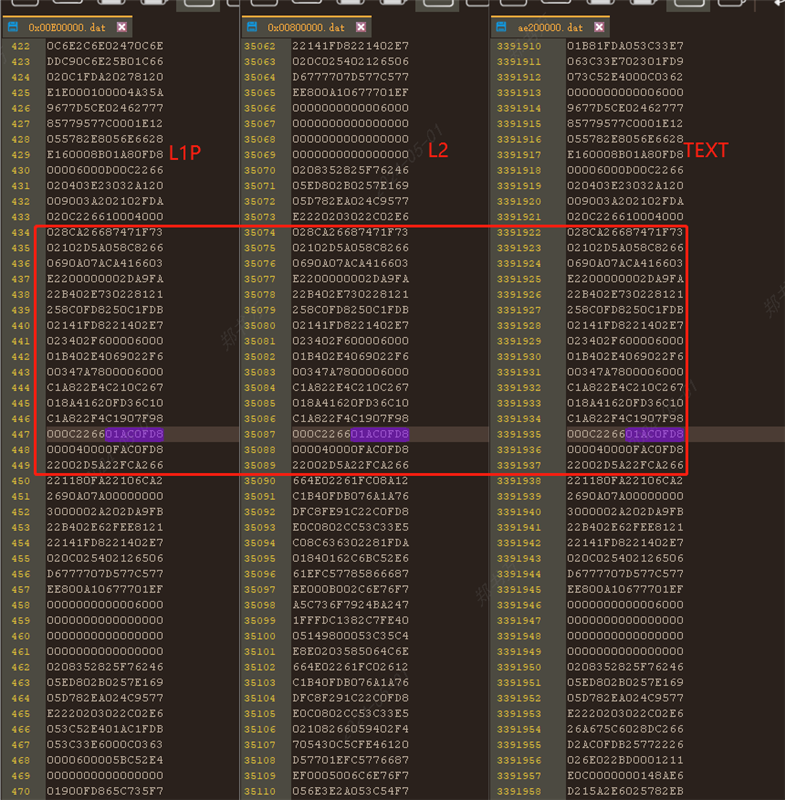

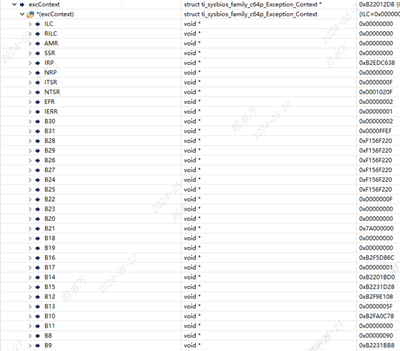

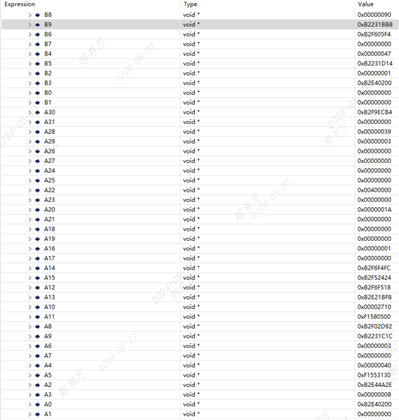

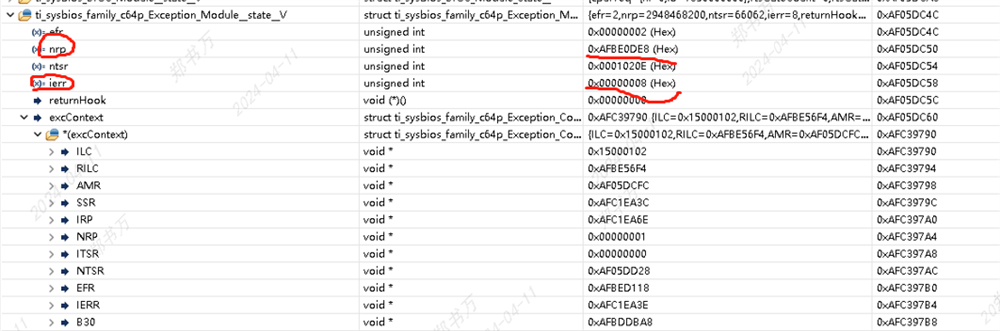

2. When using ROV Tool look more information, find the data of ti_sysbios_c64p_Exception_Module__state_V.exConText is error,show as fllows.

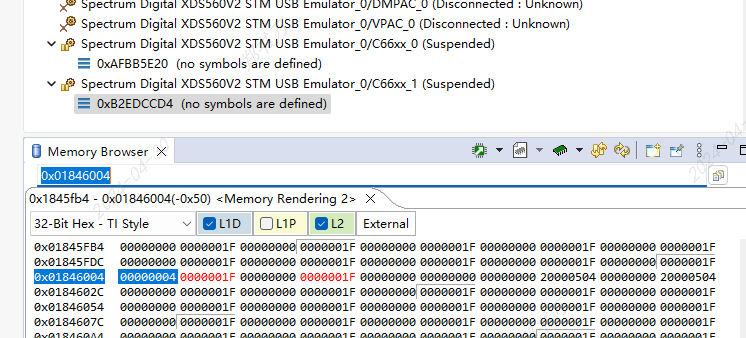

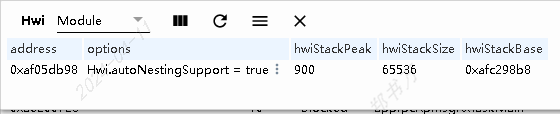

4. the exConText address is the HWI stack range(base:0xAFC298B8,size:64KB), and the contech data is saved when expception handler.

3. So, we consulted TI experts about why the C660 opcode exception occurred and the exContext data was incorrect?Currently, we are unable to find any further information and require TI's assistance.