- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi support,

I am from vector China. I would like to inquire about RAT-related content.

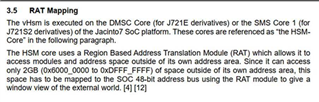

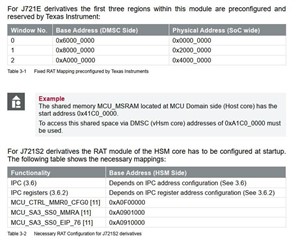

Currently, we are testing the vector secure boot solution based on TDA4VM88. However, we encountered issues when the DMSC core accessed the DDR0 region. In Vector’s HSM integration hints document, it is mentioned that in TDA4, we need to use RTA mapping to perform address mapping between the HSM core and other cores. As shown in the diagram as below.

during the secure boot process, the HSM core (DMSC) needs to read data from the corresponding region in R5 core (located in DDR0) to compute the CMAC. Since the DMSC core can only access the region from 0x60000000 to 0xDFFFFFFF, we need to map the addresses in the SoC accordingly. However, for DDR0, the addresses range from 0x97000000 to 0x97FFFFFF. How should we map the corresponding regions to ensure that the DMSC core can access data in DDR0?

Thanks and have a nice day!

Best Regards,

Yaoyao