Other Parts Discussed in Thread: AM625

I am attempting to load U-Boot via Ethernet.

I have downloaded SDK 9.02.01.09 (March 2024) and have built the new binaries with the following config files:

- am62x_evm_r5_ethboot_config

- am62x_evm_a53_defconfig

I have also tried the patch "Add-support-for-Ethernet-Boot-on-SK-AM62.patch". Many of these changes were already found in the SDK source code.

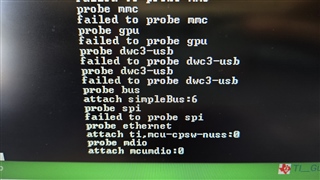

tiboot3.bin is transferring to the target board, but the last packet is not getting acknowledged and tispl.bin and u-boot.img are not being loaded.

Am I building the tiboot3.bin incorrectly?