Other Parts Discussed in Thread: J784S4XEVM

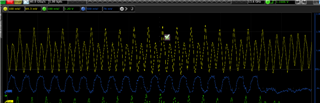

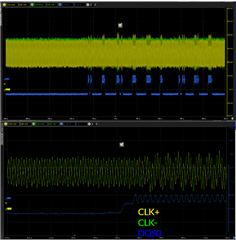

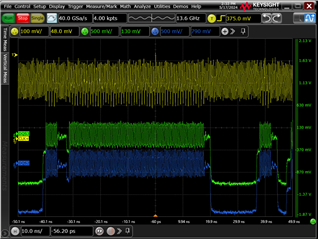

While testing the DDR CLK on our custom board to meet JDEC compliance there are failures whenever data is being transferred. As can be seen on the scope captures, whenever there is activity on the DQS line the single ended clock lines get affected. This is causing the single ended clock certification tests to fail. At first we thought it may have been power delivery related but after measuring the 1V1 line on the decoupling caps of both the processor and DDR IC there is no ripple seen. It also appears as if it could be cross talk but the only adjacent lines to the CLK in our layout are address lines and it does not appear to be coming from those. We tried to follow the EVM (J784S4XEVM) layout and decoupling scheme as much as possible and also referenced the the layout guidelines found here www.ti.com/.../spracn9e.pdf

Is there any other reasons the clock lines may be behaving like this or are there any other designs that have experienced this behavior?