Other Parts Discussed in Thread: SYSCONFIG, TDA4VH

Tool/software:

Hi, experts

My SDK version:

linux: ti-processor-sdk-linux-adas-j784s4-evm-09_01_00_06

rtos: ti-processor-sdk-rtos-j784s4-evm-09_01_00_06

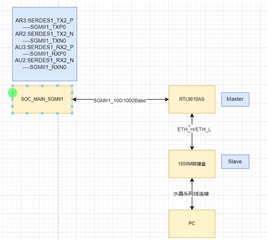

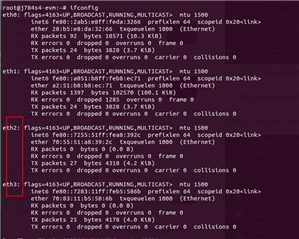

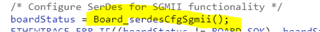

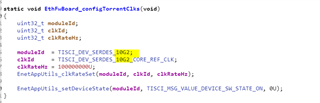

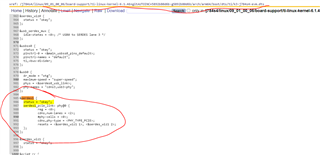

I tried to use the SGMII driver to communicate with the RTL9010A, but couldn't Link up.

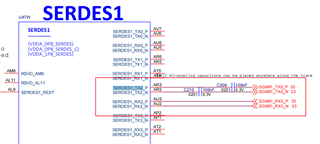

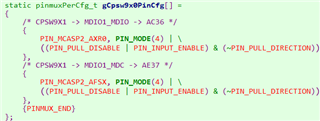

In addition, after I configured the pin through the sysconfig tool, I could not find the corresponding pin pin configuration in the generated file(J784S4_pinmux_data.c/devicetree.dtsi).

Only MDC/MDIO pin configurations are available

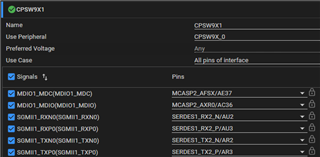

my pinMux config:

How can I use SGMII1? Is there any sample code?

Best regards