Tool/software:

I am trying to configure the VPU clock, what information is relevant to doing so?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I am trying to configure the VPU clock, what information is relevant to doing so?

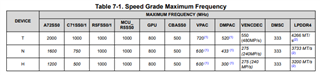

The default clock on the Linux SDK are set with these ceiling values that round up to the nearest operating frequency based on the required frequency calculated by the Wave5 VPU driver. There are some modifications in these speed grade tables that are important to take note of.

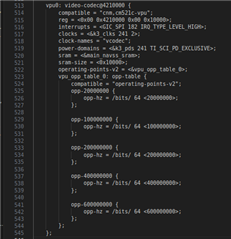

Based on the device type and speed grade from the above information, you now need to configure your device's VPU clock to the associated value. This is done by deleting the default upper limit entries of the frequency operating table that is located in arch/arm64/boot/dts/ti/k3-j721s2-main.dtsi or arch/arm64/boot/dts/ti/k3-j784s4-main.dtsi depending on the device being used.

To set the VPU clock to have an upper limit of 300MHz, change the table to the following:

To have these changes take effect, run make dtbs at the highest level of the linux kernel directory make the new device tree binary. Then copy arch/arm64/boot/dts/ti/k3-j784s4-evm.dtb or arch/arm64/boot/dts/ti/k3-j721s2-common-proc-board.dtb to the root partition in /media/user/root/boot/dtb/ti.

On boot, the device's default is 600MHz. However, once you run an encode/decode process the changes will take effect and set the limit on the CODEC clock frequency.

The J72s1s2 only has a single instance of the VPU, therefore you only need to check one clock. This can be done by utilizing the k3conf tool with the following command:

The J784s4 has two instances of the VPU, and therefore two clocks to verify. This can be done with the following command using the k3conf tool:

By default since the 9.1 SDK the VPU has clock gating enabled to dynamically set the clock based on the current VPU operation. Therefore, when the VPU is not being used it will keep the clock running at 20MHz unless dictated otherwise by the frequency table in the device tree. This also means when verifying the clock with the k3conf dump clock commands, you will have to ssh to the board and run the command simultaneously as when the CODEC operation is happening.