Other Parts Discussed in Thread: SYSBIOS

Tool/software:

Hi, dear TI engineer.

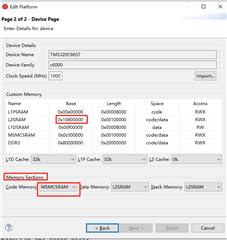

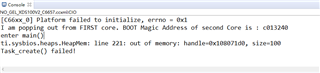

Problem describe: I'm doing some SysBios project test: After core 0 wake Core1, then creat a simple task to printf some words. But when followed the code step by step, the console shows me Task_creat fail and the HeapMem out of memory!!

Project info: I use ccs 9.3 creat a typical SYS/BIOS project, referenced Core 0 wake up the second core articles on TI forums:

Keystone Bootloader Resources and FAQ (ti.com) Section 4.14

Form these articles, I test core 0 wake up core 1 successully without SYS/BIOS.

But when I test in RTSC project, the problem appearing.

The test 1st step is core 0 wake up core core1, and creat a task, In the task diff core printf diff message.

Project Demo Pack :RTSC_MUTIPLE_BOOT.zip

RTSC part :mc2_c6657.zip

My doubt is whether my code logic is incorrect? Is there any demo project about mutiple core single image code ?