- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello TI exprits,

In the BYD SA5 we meet a very strange issue,we configurated the main domain MSRam,

in the previous tikets we have mentioned that.

and we put some text section in the 0x80000 which we congfigured in the RAT function

#define CSL_MCU_ARMSS_RAT_CFG_BASE (0x40f90000UL)

#define MSRAM_RAT_REGION_INDEX 10U

#define MSRAM_RAT_REGION_BASE (0x4F02000000UL)

#define MSRAM_RAT_REGION_SIZE (0x80000UL)

#define MSRAM_RAT_REGION_LOCAL_BASE (0x80000UL)

void Rat_Msram512KBInit(void)

{

bool ratRetVal;

CSL_RatTranslationCfgInfo translationCfg;

uint32_t index = MSRAM_RAT_REGION_INDEX;

/* Add RAT configuration to access address > 32bit address range */

translationCfg.translatedAddress = MSRAM_RAT_REGION_BASE;

translationCfg.sizeInBytes = MSRAM_RAT_REGION_SIZE;

translationCfg.baseAddress = (uint32_t)MSRAM_RAT_REGION_LOCAL_BASE;

ratRetVal = CSL_ratConfigRegionTranslation((CSL_ratRegs *)CSL_MCU_ARMSS_RAT_CFG_BASE,

index, &translationCfg);

if (ratRetVal == false) {

UART_printf("\nFailed to configure the RAT index %d address 0x%lx\n", index, translationCfg.translatedAddress);

}

}00080000 00080000 00033020 00033020 rwx 00080000 00080000 00033020 00033020 rwx .main_Msram

but currently we do some stress test and found that,some times when the sbl to copy the data from scratch memory to the main domain msram

some of the text is not correct which load in the main domain MSARAM,but the text in the DDR and mcu msam is all correct.

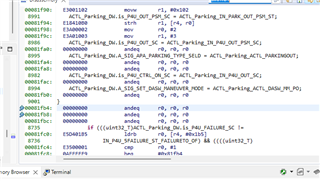

such as the text in the 0x81fb4 should be

which the correct data is like bellows

81f9c: 03 10 a0 e3 mov r1, #3

; ACTL_Parking_DW.is_P4U_OUT_SC = ACTL_Parking_IN_P4U_OUT_PSM_SC;

81fa0: c1 01 c4 e5 strb r0, [r4, #449]

; ACTL_Parking_DW.A_SIG_APA_PARKING_TYPE_SELD = ACTL_Parking_ACTL_PARKINGOUT;

81fa4: a5 01 c4 e5 strb r0, [r4, #421]

81fa8: 01 00 a0 e3 mov r0, #1

; ACTL_Parking_DW.is_P4U_CTRL_ON_SC = ACTL_Parking_IN_P4U_OUT_SC;

81fac: b1 11 c4 e5 strb r1, [r4, #433]

; ACTL_Parking_DW.A_SIG_SET_DASW_MANEUVER_MODE = ACTL_Parking_ACTL_DASW_MM_PO;

81fb0: 9c 01 c4 e5 strb r0, [r4, #412]

; }

81fb4: 34 d0 8d e2 add sp, sp, #52

81fb8: f0 8f bd e8 pop {r4, r5, r6, r7, r8, r9, r10, r11, pc}

81fbc: 00 f0 20 e3 nop

; if (((uint32_T)ACTL_Parking_DW.is_P4U_FAILURE_SC !=

81fc0: b5 01 d4 e5 ldrb r0, [r4, #437]

; IN_P4U_5FAILURE_ST_FAILURETO_OF) && ((((uint32_T)

81fc4: 01 00 50 e3 cmp r0, #1and I read the memory directly and found that there are 32bytes from 0x81fa0 to 0x81fbc which have been change to 0,

and we also check the text in the main domain MSRAM,

there are many place which have been changed

such as here

such as here

such as here

and all changed is 32 bytes which should be text code but was change to 0,is there any cache issue or dma issue?

can we use the main domain SRAM for the mcu text code.Could you pls check is this methods which use main domain MSRAM in mcu domain is fine,can you check this with your IP design TEAM for this.

Hello TI experts,

it seems that when we change the MPU configuration of the main domain msram,the situation was gone.

but in the SBL code,after each section copy there will be a SBL_DCacheClean function to make sure the cache was write back to the memory.

fp_readData((void *)(uintptr_t)(section.addr), srcAddr, section.size);

#if defined(BUILD_MCU1_0)

SBL_DCacheClean((void *)(uintptr_t)(section.addr), section.size);

#endifbut actully in the situation this seems does not work with the main domain MSRAM.Why will this issue happened and is it safe that using the main domain msram in mcu domain by using RAT translate module?

Hello Han,

Essentially, above change will make the region as non-cached, so it seems the issue is related to cache. What's the address that you are using in the cache clean function? Is it the RAT mapped address or original physical address?

Regards,

Brijesh

Hello jadav,

from TI's source code I think it will be the RAT address not the original physical address,when the sbl get the section then the

static int32_t SBL_RprcImageParse(void *srcAddr,

uint32_t *entryPoint,

int32_t CoreId)

{

rprcFileHeader_t header;

rprcSectionHeader_t section;

uint32_t sbl_rsvd_mem_start = (uint32_t)(SBL_SCRATCH_MEM_START);

uint32_t sbl_rsvd_mem_end = (uint32_t)(((uint32_t)(SBL_SCRATCH_MEM_START)) + ((uint32_t)(SBL_SCRATCH_MEM_SIZE)));

uint32_t i;

int32_t retVal = E_PASS;

uint32_t atcmSize;

uint32_t btcmSize;

const uint32_t SocAtcmAddr[] =

{

#if (SBL_USE_DMA && (defined(SOC_J721E) || defined(SOC_J7200) || defined(SOC_J721S2) || defined(SOC_J784S4)))

/* Use SoC level address of MCU1_0 ATCM for non-CPU writes to this TCM. */

SBL_MCU1_CPU0_ATCM_BASE_ADDR_SOC,

#else

SBL_MCU_ATCM_BASE,

#endif

SBL_MCU1_CPU1_ATCM_BASE_ADDR_SOC,

SBL_MCU2_CPU0_ATCM_BASE_ADDR_SOC,

SBL_MCU2_CPU1_ATCM_BASE_ADDR_SOC,

SBL_MCU3_CPU0_ATCM_BASE_ADDR_SOC,

SBL_MCU3_CPU1_ATCM_BASE_ADDR_SOC,

SBL_MCU4_CPU0_ATCM_BASE_ADDR_SOC,

SBL_MCU4_CPU1_ATCM_BASE_ADDR_SOC

};

const uint32_t SocBtcmAddr[] =

{

#if (SBL_USE_DMA && (defined(SOC_J721E) || defined(SOC_J7200) || defined(SOC_J721S2) || defined(SOC_J784S4)))

/* Use SoC level address of MCU1_0 BTCM for non-CPU writes to this TCM. */

SBL_MCU1_CPU0_BTCM_BASE_ADDR_SOC,

#else

SBL_MCU_BTCM_BASE,

#endif

SBL_MCU1_CPU1_BTCM_BASE_ADDR_SOC,

SBL_MCU2_CPU0_BTCM_BASE_ADDR_SOC,

SBL_MCU2_CPU1_BTCM_BASE_ADDR_SOC,

SBL_MCU3_CPU0_BTCM_BASE_ADDR_SOC,

SBL_MCU3_CPU1_BTCM_BASE_ADDR_SOC,

SBL_MCU4_CPU0_BTCM_BASE_ADDR_SOC,

SBL_MCU4_CPU1_BTCM_BASE_ADDR_SOC

};

const uint32_t SocC66xL2SramAddr[] =

{

SBL_C66X1_L2SRAM_BASE_ADDR_SOC,

SBL_C66X2_L2SRAM_BASE_ADDR_SOC

};

const uint32_t SocC66xL1DmemAddr[] =

{

SBL_C66X1_L1DMEM_BASE_ADDR_SOC,

SBL_C66X2_L1DMEM_BASE_ADDR_SOC

};

const uint32_t SocC7xL2SramAddr[] =

{

SBL_C7X1_L2SRAM_BASE_ADDR_SOC,

SBL_C7X2_L2SRAM_BASE_ADDR_SOC

};

const uint32_t SocC7xL1DmemAddr[] =

{

SBL_C7X1_L1DMEM_BASE_ADDR_SOC,

SBL_C7X2_L1DMEM_BASE_ADDR_SOC

};

const uint32_t SocM4fIramAddr[] =

{

SBL_M4F_IRAM_BASE_ADDR_SOC

};

const uint32_t SocM4fDramAddr[] =

{

SBL_M4F_DRAM_BASE_ADDR_SOC

};

const uint32_t SocHsmM4fDramAddr[] =

{

SBL_HSM_M4F_SRAM_BASE_ADDR_SOC

};

/*read application image header*/

fp_readData(&header, srcAddr, sizeof (rprcFileHeader_t));

/*check magic number*/

if (header.magic != RPRC_MAGIC_NUMBER)

{

SBL_log(SBL_LOG_ERR, "Invalid magic number in boot image. Expected: %x, received: %x\n", RPRC_MAGIC_NUMBER, header.magic);

retVal = E_FAIL;

}

else

{

/* Set the Entry Point */

*entryPoint = header.entry;

/* Setup CPUs internal memory before using it */

SBL_SetupCoreMem(CoreId);

/* Remap virtual core-ids if needed */

switch (CoreId)

{

case MCU2_SMP_ID:

CoreId = MCU2_CPU0_ID;

break;

case MCU3_SMP_ID:

CoreId = MCU3_CPU0_ID;

break;

case MCU4_SMP_ID:

CoreId = MCU4_CPU0_ID;

break;

default:

break;

}

/*read entrypoint and copy sections to memory*/

for (i = (0U); i < header.SectionCount; i++)

{

fp_readData(§ion, srcAddr, sizeof (rprcSectionHeader_t));

switch (CoreId)

{

#if (SBL_USE_DMA && defined(BOOT_OSPI) && (defined (SOC_J721E) || defined(SOC_J7200) || defined(SOC_J721S2) || defined(SOC_J784S4)))

/* Need address translation to SoC level addresses of MCU1_0 TCMs, when trying to copy to local addresses */

case MCU1_CPU0_ID:

atcmSize = sblAtcmSize();

btcmSize = sblBtcmSize();

/* Only do TCM addr remapping for MCU1_0 if using UDMA for transfers from OSPI to local TCMs */

if (fp_readData == SBL_OSPI_ReadSectors)

{

/*Remap TCM address from R5 local to SoC memory map*/

if (section.addr < (SBL_MCU_ATCM_BASE + atcmSize))

{

/* Get offset into ATCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local ATCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_ATCM_BASE;

section.addr = SocAtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU ATCM addr 0x%x\n", section.addr);

}

else if ((section.addr >= SBL_MCU_BTCM_BASE) &&

(section.addr < (SBL_MCU_BTCM_BASE + btcmSize)))

{

/* Get offset into BTCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local BTCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_BTCM_BASE;

section.addr = SocBtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU BTCM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

}

break;

#endif

case MCU1_CPU1_ID:

case MCU2_CPU0_ID:

case MCU2_CPU1_ID:

case MCU3_CPU0_ID:

case MCU3_CPU1_ID:

case MCU4_CPU0_ID:

case MCU4_CPU1_ID:

atcmSize = sblAtcmSize();

btcmSize = sblBtcmSize();

/*Remap TCM address from R5 local to SoC memory map*/

if (section.addr < (SBL_MCU_ATCM_BASE + atcmSize))

{

/* Get offset into ATCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local ATCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_ATCM_BASE;

section.addr = SocAtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU ATCM addr 0x%x\n", section.addr);

}

else if ((section.addr >= SBL_MCU_BTCM_BASE) &&

(section.addr < (SBL_MCU_BTCM_BASE + btcmSize)))

{

/* Get offset into BTCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local BTCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_BTCM_BASE;

section.addr = SocBtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU BTCM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

break;

case DSP1_C66X_ID:

case DSP2_C66X_ID:

/*Remap L1 & L2 address from C66x local to SoC memory map*/

if ((section.addr >= SBL_C66X_L2SRAM_BASE) &&

(section.addr < (SBL_C66X_L2SRAM_BASE + SBL_C66X_L2SRAM_SIZE)))

{

/* Get offset into L2 SRAM */

SBL_log(SBL_LOG_MAX, "Translating C66x local L2SRAM addr 0x%x to ", section.addr);

section.addr = section.addr - SBL_C66X_L2SRAM_BASE;

section.addr = SocC66xL2SramAddr[CoreId - DSP1_C66X_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC C66x L2SRAM addr 0x%x\n", section.addr);

}

else if ((section.addr >= SBL_C66X_L1DMEM_BASE) &&

(section.addr < (SBL_C66X_L1DMEM_BASE + SBL_C66X_L1DMEM_SIZE)))

{

/* Get offset into L1 DRAM */

SBL_log(SBL_LOG_MAX, "Translating C66x local L1DMEM addr 0x%x to ", section.addr);

section.addr = section.addr - SBL_C66X_L1DMEM_BASE;

section.addr = SocC66xL1DmemAddr[CoreId - DSP1_C66X_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC C66x L2DMEM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

break;

case DSP1_C7X_ID:

case DSP2_C7X_ID:

case DSP3_C7X_ID:

case DSP4_C7X_ID:

/*Remap L1 & L2 address from C7x local to SoC memory map*/

if ((section.addr >= SBL_C7X_L2SRAM_BASE) &&

(section.addr < (SBL_C7X_L2SRAM_BASE + SBL_C7X_L2SRAM_SIZE)))

{

/* Get offset into L2 SRAM */

SBL_log(SBL_LOG_MAX, "Translating C7x local L2SRAM addr 0x%x to ", section.addr);

section.addr = section.addr - SBL_C7X_L2SRAM_BASE;

section.addr = SocC7xL2SramAddr[CoreId - DSP1_C7X_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC C7x L2SRAM addr 0x%x\n", section.addr);

}

else if ((section.addr >= SBL_C7X_L1DMEM_BASE) &&

(section.addr < (SBL_C7X_L1DMEM_BASE + SBL_C7X_L1DMEM_SIZE)))

{

/* Get offset into L1 DRAM */

SBL_log(SBL_LOG_MAX, "Translating C7x local L1DMEM addr 0x%x to ", section.addr);

section.addr = section.addr - SBL_C7X_L1DMEM_BASE;

section.addr = SocC7xL1DmemAddr[CoreId - DSP1_C7X_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC C7x L2DMEM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

break;

case HSM_CPU_ID:

/*

* HSM entry is always specified as the local SRAM base

* (0x0000_0000)

*/

*entryPoint = 0U;

/* Remap HSM local address to SoC address */

if ((section.addr >= 0U) &&

(section.addr < (SBL_HSM_M4F_SRAM_SIZE)))

{

SBL_log(SBL_LOG_MAX, "Translating HSM local SRAM addr 0x%x to ", section.addr);

section.addr = SocHsmM4fDramAddr[0U] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC HSM SRAM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

break;

default:

break;

}

if ((fp_readData == SBL_ReadMem) &&

(((section.addr > sbl_rsvd_mem_start) && (section.addr < sbl_rsvd_mem_end)) ||

(((section.addr + section.size) > sbl_rsvd_mem_start) && ((section.addr + section.size) < sbl_rsvd_mem_end))))

{

SBL_log(SBL_LOG_ERR, "Warning!! Section overwrites SBL reserved memory\n");

retVal = E_FAIL;

}

else

{

SBL_log(SBL_LOG_MAX, "Copying 0x%x bytes to 0x%x\n", section.size, section.addr);

fp_readData((void *)(uintptr_t)(section.addr), srcAddr, section.size);

#if defined(BUILD_MCU1_0)

SBL_DCacheClean((void *)(uintptr_t)(section.addr), section.size);

#endif

}

}

}

return retVal;

}Hello Han,

But the above code does not take care of the newly added RAT mapping, isn't it? There is a code to map ATCM and BTCM memories, not OCM memory.

Regards,

Brijesh

you mean this code?so the cache clean function input address must be the physic address right?

case MCU4_CPU1_ID:

atcmSize = sblAtcmSize();

btcmSize = sblBtcmSize();

/*Remap TCM address from R5 local to SoC memory map*/

if (section.addr < (SBL_MCU_ATCM_BASE + atcmSize))

{

/* Get offset into ATCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local ATCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_ATCM_BASE;

section.addr = SocAtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU ATCM addr 0x%x\n", section.addr);

}

else if ((section.addr >= SBL_MCU_BTCM_BASE) &&

(section.addr < (SBL_MCU_BTCM_BASE + btcmSize)))

{

/* Get offset into BTCM */

SBL_log(SBL_LOG_MAX, "Translating coreid %d local BTCM addr 0x%x to ", CoreId, section.addr);

section.addr = section.addr - SBL_MCU_BTCM_BASE;

section.addr = SocBtcmAddr[CoreId - MCU1_CPU0_ID] + section.addr;

SBL_log(SBL_LOG_MAX, "SoC MCU BTCM addr 0x%x\n", section.addr);

}

else

{

/* To remove MISRA C error */

}

break;but the main domain physic address is 64bit adress

Hello Han,

Yes, that's true that we cannot access 48bit address on R5F and that's why we need to use RAT mapped address when CPU is trying to access this memory.

This is why this code requires a slight change that when it is copying second to this OCM memory, it needs to use RAT mapped address, this is not taken care in the current SBL and you would need to this code.

Can you please first confirm that this change has been in the RPRC parser code in the SBL?

Regards,

Brijesh

Hello Jadav,

there must be some mistakes, in our mcu linker file, we already make it to rat address not the physic address,which makes the SBL_DChacheClean function input address is already the RAT address I think.