Tool/software:

Hello TI Experts,

We have a custom HW based on AM69 SOC and would like to use SOC DSI0 with LT8912B bridge for HDMI connector.

I am bringing up AM69 DSI0 and LT8912B bridge chip for DSI to HDMI conversion. During my tests, I observed that DSI CLK is at-least available at ~119 MHz for my test resolution 800x600, however on the DSI0 data lanes, I do not see any data. Data lines stays high at ~1.8V.

I tried to check the DSI0 status register and it matches somewhat with my observations on oscilloscope. DSI CLK is in HS mode, data lines are in data-ready state.

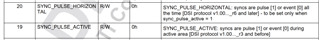

root@aquila-am69-12345678:~# devmem2 0x0480002C /dev/mem opened. Memory mapped at address 0xffff81582000. Read at address 0x0480002C (0xffff8158202c): 0x000402A6

I am using the fix EDID blob of 800x600 resolution to begin with. (I believe that same fixed resolution is present for J784s4 EVM where DSI to eDP bridge chip is present -> https://git.ti.com/cgit/ti-linux-kernel/ti-linux-kernel/commit/?h=ti-linux-6.1.y&id=50b06eec44cdae252de3154517333dca90394b12 )

Could you please let me know why there's no data on DSI0 lanes ? What could be missing in my configuration ?

From SW side, I do not see any obvious errors. I believe something might not be right in my configuration. No display at bootup even Weston is started. Modetest does not show any test pattern too. This is obvious considering the fact that there's no data from DSI0 is being transmitted.

SW details:

DTS

- https://git.toradex.com/cgit/linux-toradex.git/tree/arch/arm64/boot/dts/ti/k3-am69-aquila.dtsi?h=toradex_ti-linux-6.1.y

- https://git.toradex.com/cgit/linux-toradex.git/tree/arch/arm64/boot/dts/ti/k3-am69-aquila-dev.dts?h=toradex_ti-linux-6.1.y

Overlay for DSI to HDMI

Apart that, we run everything same from TI tag 09.02.00.010 from SW side.

Logs:

Modetest : /cfs-file/__key/communityserver-discussions-components-files/791/modetest_5F00_logs.txt

DRM Debug Logs: /cfs-file/__key/communityserver-discussions-components-files/791/drm_5F00_debug_5F00_logs.txt

Serial Console Logs: /cfs-file/__key/communityserver-discussions-components-files/791/serial_5F00_console_5F00_logs.txt

Thank you.

Regards,

Parth P