Tool/software:

Hi Support Team,

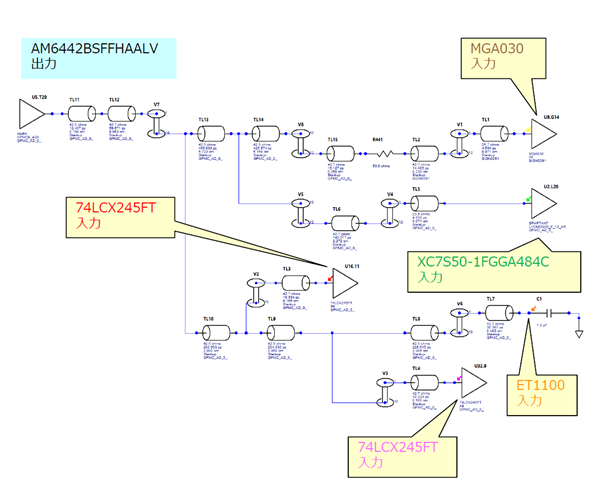

Our customer, who is doing SI Simulation, has the following question about GPMC I/F.

The waveform is not a square wave, due to the small drive strength of the IBIS model (AM64x SR2.0 BSDL Model).

The simulation is still in progress, but I wonder if the current result is correct.

If not, please let me know how to fix it.

Best Regards,

Kanae