Tool/software:

Hi,

I'm looking for a method for Booting App.bin without IBL, only using the RBL.

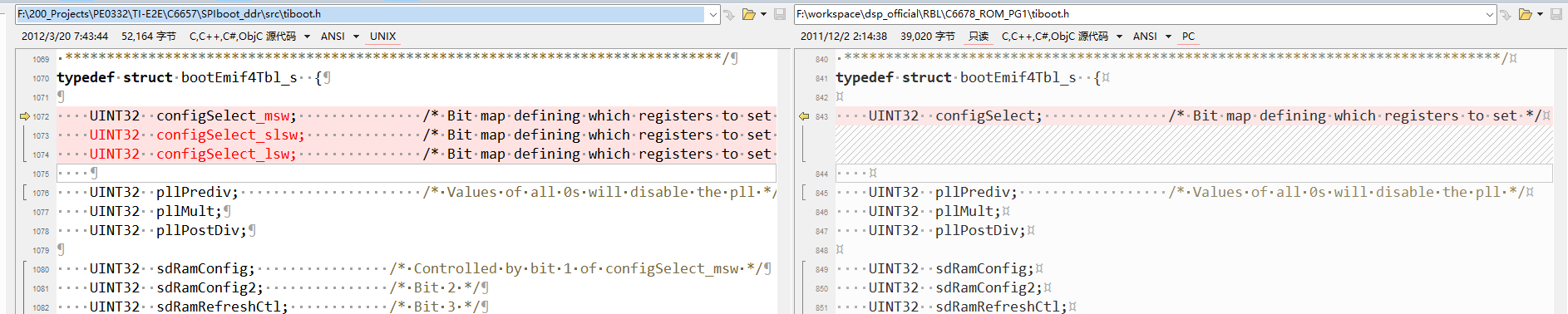

And I find a reply, under this topic :TMS320C6678: Boot from SPI NOR on Eval board using only RBL - Processors forum - Processors - TI E2E support forums but THE LINK below is Not Found! Where can I get this?

Or is there any other wiki I can follow? I'm confused in HOW to convert CCS output file app.out into SPI-NORFlash bootable format only use the RBL.

Best wishes!

Thank you