Other Parts Discussed in Thread: SYSCONFIG, AM6442, , AM6422, TMDS64EVM, SK-AM64B

Tool/software:

Hello,

I found some issues when debugging MCSPI – FRAM. Please help give solutions to resolve these issues, thanks.

Currently below configuration is used for MCSPI0.

The issues are

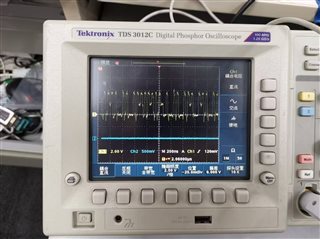

- The CLK is not regular or stable, which will cause the data to write or read is NOT correct. (channel 0 is CLK, 1 is SDI, 2 is CS, 3 is SDO)

- If CLK is set more than 7M HZ, then the clock output seems not correct as below snapshot. And MCSPI_transfer can NOT write/read correct data in all time.

- If CLK is set less than 7M HZ, the clock output is also not regular(duty cycle is variable), in this situation, MCSPI_transfer sometimes can read/write correct data, but it still will read/write error data.

FYI, below snapshot is clock waveform that captured from Oscilloscope.

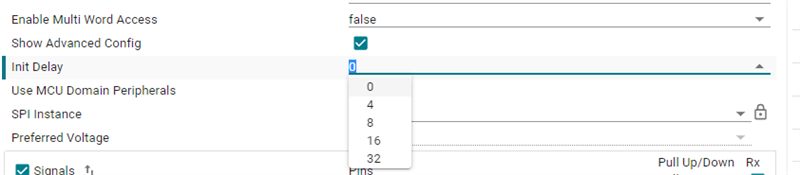

2. Another point is about MCSPI_Attrs. inputClkFreq, this parameter seems NOT can be configured in sysconfig, it is hard coded as 50M. We want to increase inputClkFreq to see if it can impact CLK output(bring it up to 30M bps)

Can you tell us where to configure it?

/* MCSPI atrributes */

static MCSPI_Attrs gMcspiAttrs[CONFIG_MCSPI_NUM_INSTANCES] =

{

{

.baseAddr = CSL_MCSPI0_CFG_BASE,

.inputClkFreq = 50000000U, // hard coded as 50M. I tried change it manually here, for example, to 200M, but it seems no effect

.intrNum = 204,

.operMode = MCSPI_OPER_MODE_INTERRUPT,

.intrPriority = 4U,

.chMode = MCSPI_CH_MODE_SINGLE,

.pinMode = MCSPI_PINMODE_4PIN,

.initDelay = MCSPI_INITDLY_0,

.multiWordAccess = FALSE,

},

};